Unsere Capabilities

Das können wir!

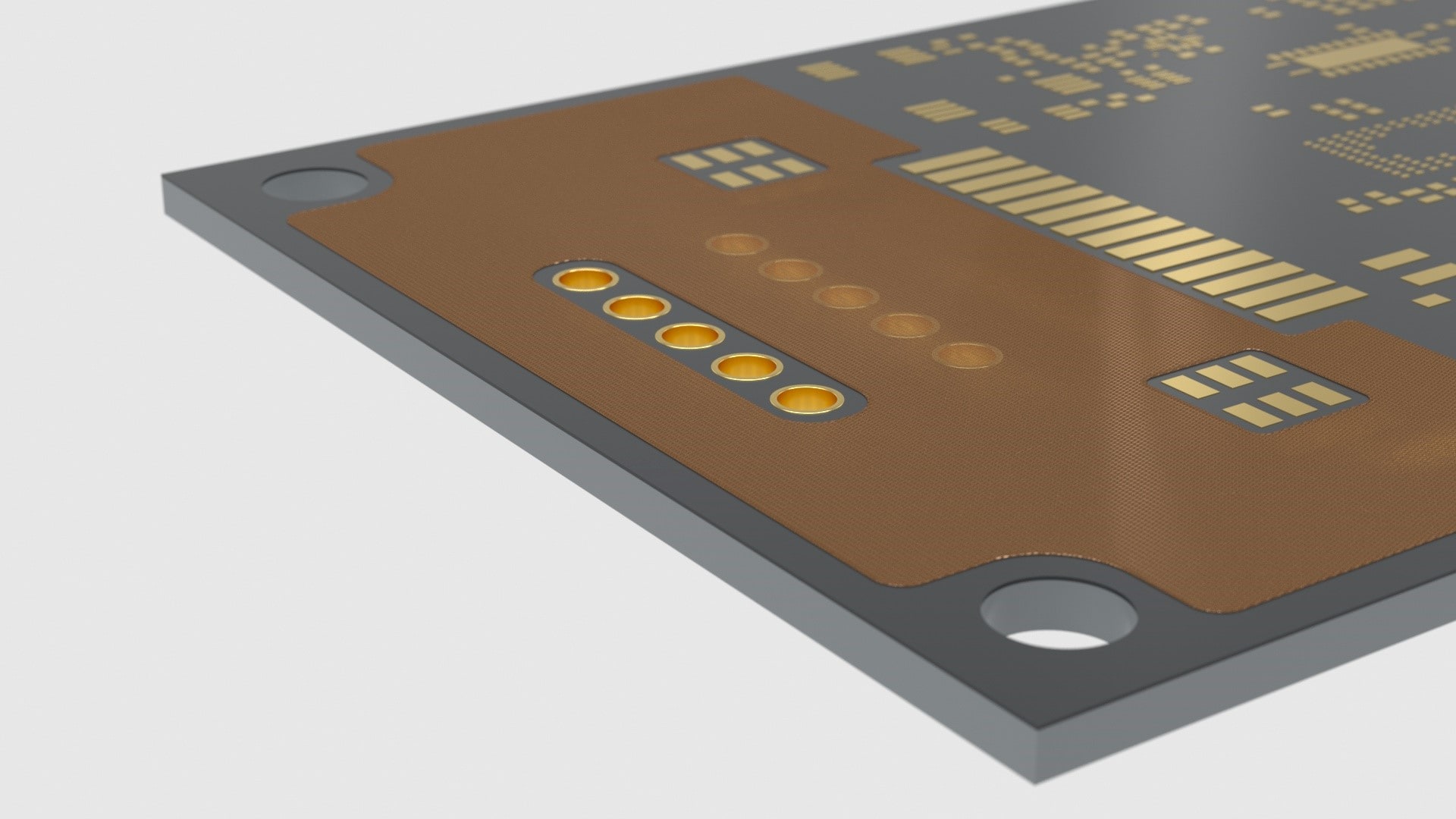

Moderne Leiterplattenlösungen sind mehr als nur Verbindungselemente. Sie sind der Schlüssel zum Fortschritt in der Elektronik. Leiterplatten sind selbst Bauteile, komplexe Konstrukte aus unterschiedlichsten Materialien. Hergestellt in einer Vielzahl von Prozessen und mit vielfältigen zu planenden Funktionen und Eigenschaften.

Würth Elektronik bietet deshalb Standards für verschiedene Leiterplatten-Technologien an und schafft damit die Grundlage für Qualität und Effizienz.

Losgelöst von allen Abhängigkeiten geben wir Ihnen hier einen ersten Überblick über die Standard-Optionen und Standard-Designparameter für Materialien und Prozesse. Dies soll und kann die persönliche Beratung nicht ersetzen. Gerne erarbeiten wir zusammen mit Ihnen eine passende Lösung für Ihr Produkt, die auch über die hier gezeigten Standards hinausgehen kann – sprechen Sie uns bitte an!

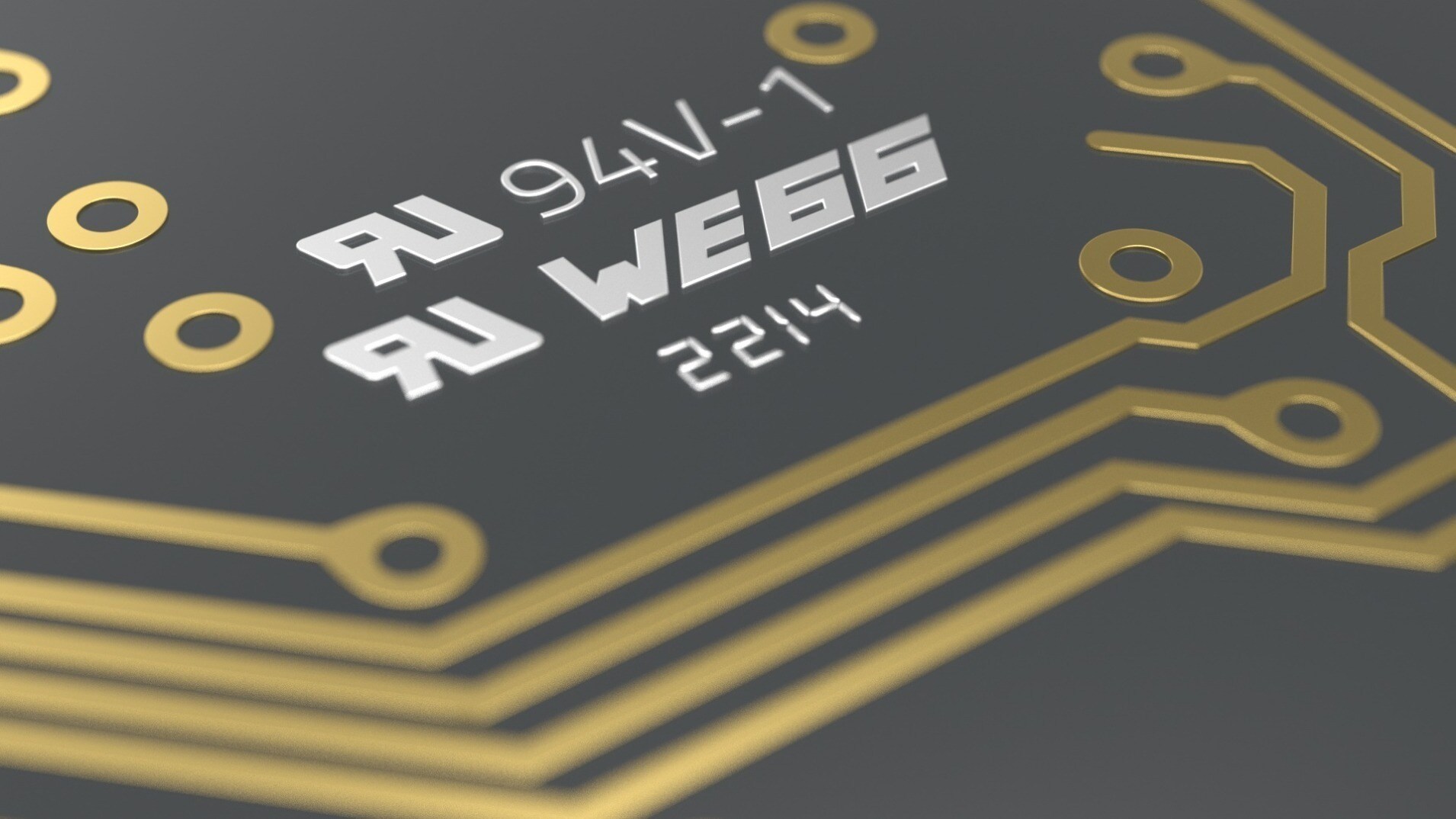

Alle eingesetzten Basismaterialien sind IPC-konform.

Starre Basismaterialien sind in der IPC-4101 und deren Spezifikationsblättern definiert. Für Standard FR-4.0 mit Tg135 gilt beispielsweise Spezifikationsblatt 21, höherwertige FR-4.1 zum Beispiel in den Spezifikationsblättern 128 (127) für erhöhte Einsatztemperaturen mit Tg150 und Low CTE (Coefficient of Thermal Expension). Abgerundet wird unser Portfolio mit CEM-1 Materialien (Spezifikationsblätter 10,15, 80) und CEM-3 Materialien (Spezifikationsblätter 12, 14, 16, 35, 81) sowie High Performance Materialien mit höherer Temperaturbeständigkeit oder Low Loss Materialien für High Speed / High Frequency Anwendungen (IPC-4103).

Flexible Basismaterialien sind in den Standards IPC-4202 / IPC-4203 und IPC-4204 spezifiziert. Unsere eingesetzten Polyimidfolien sind immer hochwertig und kleberlos.

Standardkupferfolien entsprechend IPC-4562.

Nehmen Sie bitte Kontakt mit uns auf, wenn Sie spezielle Anforderungen haben.

Erfahren Sie außerdem mehr in unserer (englischsprachigen) Webinar-Aufzeichnung "Sie haben die Wahl: STARR.flex mit Flexlack oder Coverlay?" oder in der dazugehörigen Präsentation.

Standards erleichtern unser Leben, sichern die Qualität von Produkten und Dienstleistungen und senken die Kosten. Deshalb bieten wir für viele Technologien marktübliche und kostenoptimierte Standard Stackups an. Sie können diese Standards als Basis für Ihre Lösungen verwenden und nach Ihren Anforderungen modifizieren.

Natürlich fertigen wir auch nach Ihren individuellen, projektspezifischen Stackups, nachdem wir diese auf technische Machbarkeit geprüft haben. Sprechen Sie uns an!

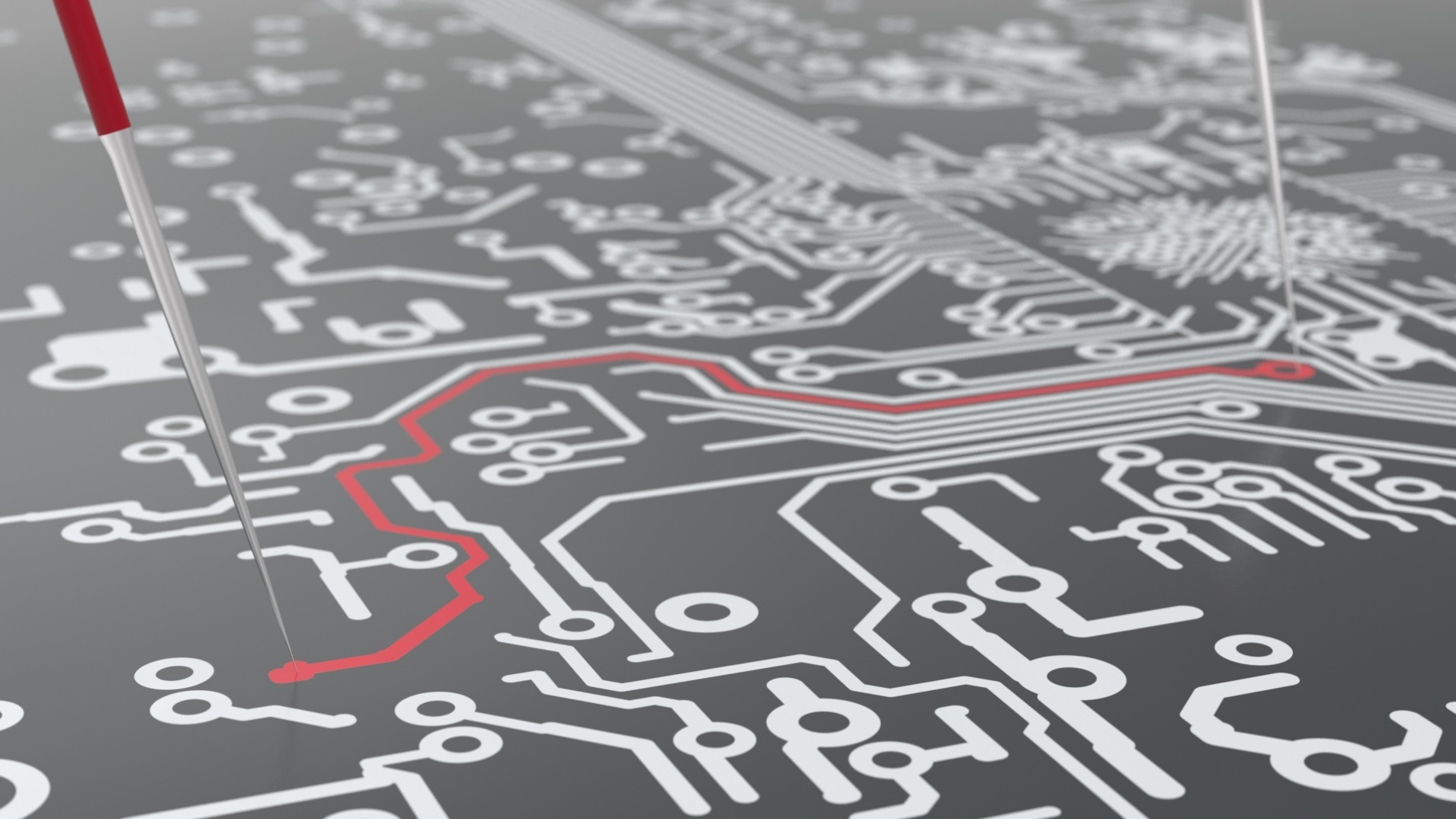

Leiterbildstrukturen auf den Innenlagen werden in Subtraktivtechnik aus der Kupferfolie mittels Ätzen erzeugt. Auf den Außenlagen bestehen Leiterbildstrukturen aus Basiskupfer plus Kupferaufbau aus den Prozessen „Durchkontaktierung“ und „Galvanische Verstärkung“.

Abhängig von den zu ätzenden Kupferschichtdicken ist die Feinheit der Strukturen begrenzt. Für die Ätzprozesse sind die Leiterabstände entscheidend. Je dünner die Kupferfolien, desto kleiner können die Isolationsabstände geätzt werden. Durch unterschiedliche Werte für Leiterbreite und Leiterabstand können Designs je nach Anforderungen elektrisch und kostentechnisch optimiert werden.

Die zugrundeliegenden technologischen Rahmenbedingungen für Leiterbildstrukturen, Bohrungen, Lötstoppmaske, Kennzeichnungen und Oberflächen sind in unseren BASIC Design Rules zusammengefasst. Diese gelten für die Basistechnologie (ein- und doppelseitige sowie Multilayer-Leiterplatten), finden jedoch ebenso Anwendung auf weiterführende Technologien wie HDI Microvia, Embedding Technology oder Flex-Lösungen. Damit bilden sie eine verlässliche Grundlage für das Design unabhängig von der späteren Leiterplattentechnologie.

Werden schnelle, digitale Signale und analoge, hochfrequente Informationen über eine Leiterplatte geleitet, müssen deren Übertragungseigenschaften betrachtet werden. Signalintegrität ist die Eigenschaft aller Arten von Leiterplatten, Signale nur in einem zulässigen Umfang zu verfälschen, so dass die Funktion der Schaltung im spezifizierten Bereich gegeben ist. Damit wird auch klar, dass Leiterplatten mit spezifizierten Signalintegritätsanforderungen maßgeschneidert designt werden müssen: Materialauswahl, Lagenaufbau und Designregeln müssen abgestimmt und spezifiziert werden. Wir bieten geeignete Materialien (siehe Rubrik "Basismaterial") an und beraten Sie gerne beim Lagenaufbau und Festlegen der Designparameter. Hybridaufbauten sind ebenso möglich.

Die TDR (Time Domain Reflectometry) Impedanzmessung ermöglicht es, Wellenwiderstände für spezifizierte Übertragungsleitungen zu messen.

Weitere Informationen zu unseren Testverfahren finden Sie hier.

Erfahren Sie außerdem mehr über Signalintegrität in unserer Webinar-Aufzeichnung "Impedanz ist für alle da!" oder in der dazugehörigen Präsentation.

Mechanische Bohrungen können unterschiedliche Funktionen erfüllen. Als elektrische und therminsche Verbindung zwischen den Lagen einer Leiterplatte werden sie leitfähig mit Kupfer metallisiert. Als Registrier- oder Befestigungsbohrung wird die Bohrungshülse nicht metallisiert (NDK = nicht durchkontaktiert oder NDM = nicht durchmetallisiert). Mit größeren Durchmessern dienen PTHs auch als Bestückbohrungen für das Einlöten von bedrahteten Bauteilen und Steckern. Eine Besonderheit stellt das lötfreie Einpressen dar, wofür eingeschränkte Bohrlochtoleranzen notwendig sind.

Mit Laser hergestellte Bohrungen sind immer Sacklochbohrungen.

Durch den Metallisierungsprozess werden aus mechanisch gebohrten Löchern PTHs oder DKs (PTH = Plated Through Hole, DK = durchkontaktierte Bohrung), aus lasergebohrten Löchern werden Microvias. Ein wichtiger Parameter beim Design von Bohrungen ist das Verhältnis Bohrdurchmesser zu Lochtiefe: das Aspect Ratio.

PTHs und Microvias müssen für den elektrischen Kontakt Viapads aufweisen, die natürgemäß bei Microvias deutlich kleiner sind und auch in Lötflächen von Bauelementen integriert sein können.

Im Zuge der fortschreitenden Miniaturisierung in der Elektronik wachsen auch die Anforderungen an Via-Bohrungen. Sie dienen nicht nur der elektrischen Durchverbindung, sondern haben entscheidende Bedeutung zum Beispiel hinsichtlich Bestückbarkeit, Zuverlässigkeit und Wärmeableitung.

In der Aufzeichnung und der dazugehörigen Präsentation unseres Webinars "Plugging - Filling - Tenting" erhalten Sie einen Einblick in die Verknüpfung des PCB Designs mit den Auswirkungen für die Leiterplattenfertigung und den dabei anfallenden Kosten. Wir geben Hinweise auf die generelle Kostenstruktur einer Leiterplatte mit Blick auf deren Layout und Geometrie.

Unser Standard für Lötstoppmasken sind grüne, photosensitive Lötstopplacke, die die Anforderungen der IPC-SM-840 Class T und H erfüllen. Andere Farben wie weiß, schwarz, blau, rot oder gelb sind auf Anfrage möglich. Die Ausführung werden je nach Produktionsstandort als farbiger Lötstopplack anstelle des grünen Lötstopplacks oder als Zusatzdruck über den grünen Standardlack ausgeführt.

Bestückungsdrucke und Kennzeichnungen erfolgen vorzugsweise in weißer Tinte auf Lötstopplack, andere Farben sind möglich.

Für die Beschichtung setzen wir alle marktüblichen Technologien ein (Siebdruck, Vorhanggießen, Sprühen). Schon heute fertigen wir Lötstoppmasken für innovative Produkte in Additivtechnik im Inkjet-Verfahren. Weitere Informationen zu diesem Verfahren erhalten Sie in der Aufzeichnung zu unserem Webinar "Additiver Serienprozess für flexiblen Lötstopplack – unser neuer Standard" oder in der dazugehörigen Präsentation.

Zur Sicherstellung der Lötbarkeit werden freiliegende Kupferflächen mit einer Lötoberfläche versehen. Mehr Informationen dazu finden Sie in unserer Technischen Lieferspezifikation für Leiterplatten, Kapitel 3.1.

Webinar-Tipp: Lötoberflächen im Fokus

Ob einfache BASIC-Leiterplatte oder komplexe STARR.flex-Technologie – jede Anwendung stellt individuelle Anforderungen an die passende Endoberfläche. Unser Webinar-Aufzeichnung zeigt, worauf es bei der Auswahl ankommt, welche Möglichkeiten es gibt und warum das Thema Lagerfähigkeit nicht unterschätzt werden sollte.

Für spezielle Anforderungen wie zum Beispiel "Schleifkontakte" bitten wir um Rücksprache.

Die Bearbeitung der Kontur Ihrer Leiterplatten - auch im Liefernutzen - kann durch Kerben, Fräsen oder durch eine Kombination aus Kerben und Fräsen ausgeführt werden. Flexible Leiterplatten oder Bereiche können mit Laser getrennt werden.

Gerne unterstützen wir Sie im Design einer optimalen Liefernutzengestaltung. Direktstecker können angefast werden. Details dazu finden Sie in unserer Technischen Lieferspezifikation für Leiterplatten.

Für Kantenmetallisierung ist vor der Metallisierung ein zusätzlicher Fräsprozess notwendig.

Die Möglichkeiten einer Liefernutzengestaltung entnehmen Sie bitte unserer Technischen Lieferspezifikation für Leiterplatten, Kapitel 2.4.

Durch eine Optimierung des Liefernutzens kann unser Produktionspanel oft besser und nachhaltiger ausgenutzt werden und führt zu spürbaren Preisoptimierungen. Sprechen Sie uns an.

Die Anforderungen an elektrische Baugruppen steigen stetig. Einerseits werden durch Kosten- und Zeitdruck kürzere Entwicklungszeiten für Produkte gefordert. Andererseits werden hohe Anforderungen an die Zuverlässigkeit von Baugruppen aufgrund der Einsatzbedingungen gestellt. Zudem werden hochwertige Komponenten verbaut, die nur kostspielig und mit langer Vorlaufzeit wiederzubeschaffen sind. Auch die Leiterplatte selbst spielt für die Zuverlässigkeit eine entscheidende Rolle. Alternative Lösungsansätze müssen bezüglich der Zuverlässigkeit bewertet und die Entscheidungen durch Tests verifiziert werden.

Weitere Informationen zu unseren Testverfahren finden Sie hier.

Als Standard fertigen wir nach IPC-A-600 Klasse 2. Auf Anfrage erhalten Sie Klasse 3 mit und ohne Testdokumentation.

Coverlay, ein Verbundmaterial aus Polyimidfolie und Kleber, kann als Isolation auf bestimmte Bereiche einer Leiterplatte aufgeklebt werden. Dadurch lassen sich hohe Durchschlagsfestigkeiten ereichen.

Welche Design Rules berücksichtigt werden müssen, können Sie hier erfahren.

Sie möchten noch mehr über den Einsatz von Coverlay als Isolationsfolie lernen?

Dann schauen Sie hier die Aufzeichnung und die Präsentation unseres Webinars "Deckfolien – mehr als ein flexibler Lötstopplackersatz" an:

Ihr Kontakt zu uns