# Anticipate EMC with LTSPICE

Anticipate EMC with LTSpice Using LTSPICE and Redexpert to check power supply designs

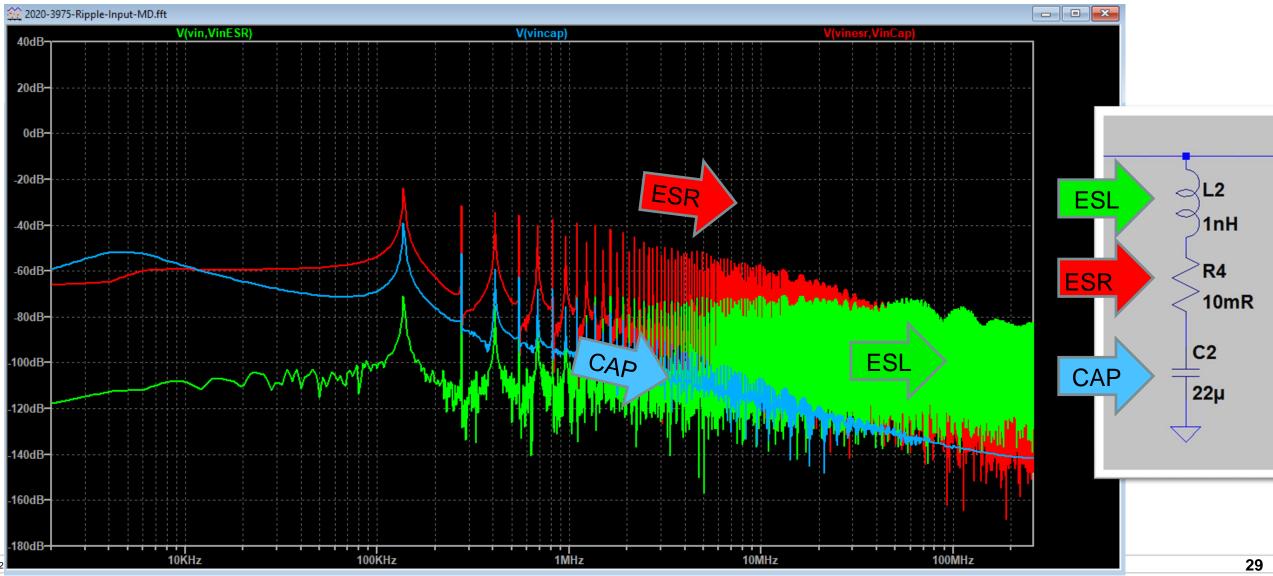

- Intro : From functional simulation...

- Output ripple of a Buck

- Extracting EMC accurate data from REDEXPERT

- Example of (non) EMC accurate impact on simulation

#### Interpretation Interpretation

- Enabling EMC measurement in LTSpice

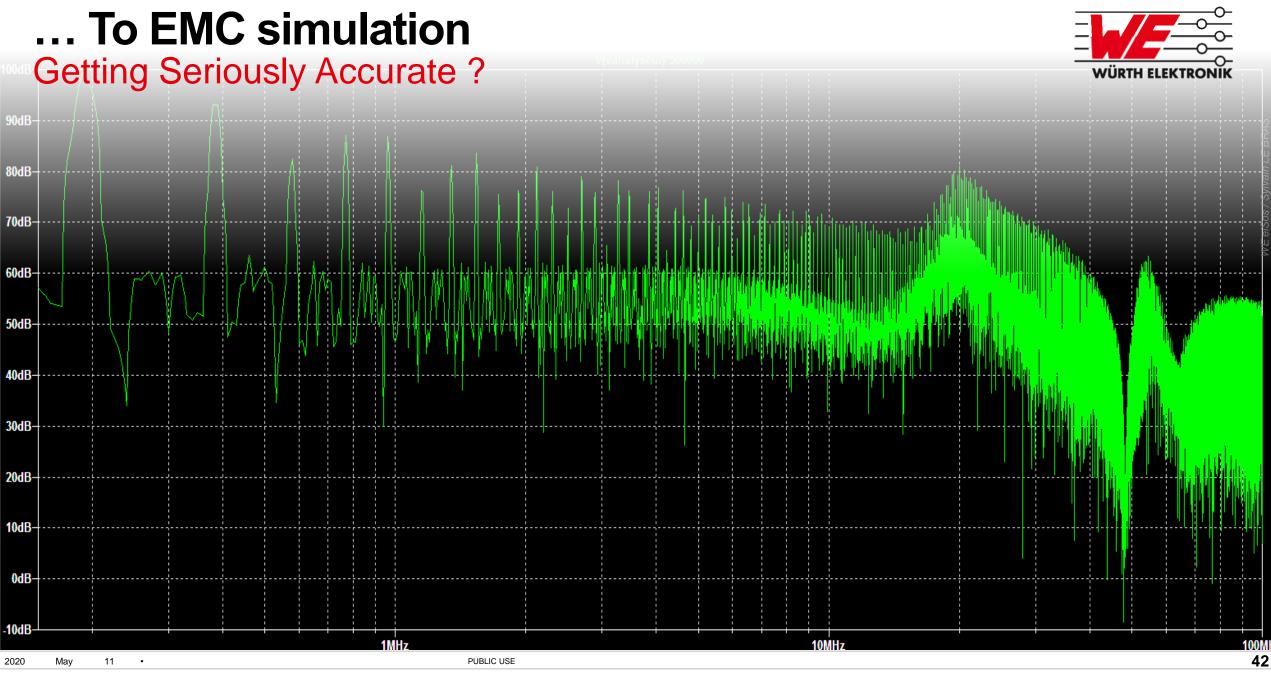

- Getting Seriously Accurate ?

- Going further with simulation

- Splitting Common and Differential mode

- Making simulation look real

- Examples

TA\_Master2020A\_Agenda0\_0

Anticipate EMC with LTSpice Using LTSPICE and Redexpert to check power supply designs

#### Available examples

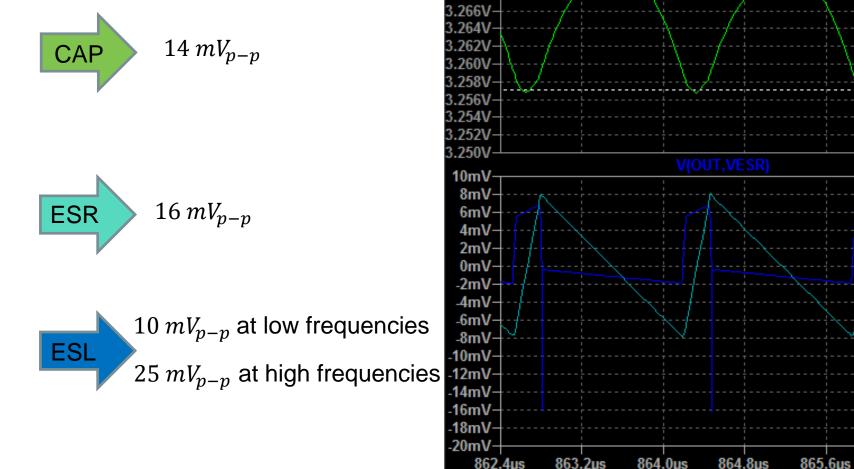

- Output ripple of a Buck Individual contribution of parasitics 1.

- 2. Noise at Input of Buck – Concept of Stabilized impedance

- 3. Noise at Input of Buck – Concept CM return path and DM/CM split

- Flyback converter Stray inductance and interwinding capacitance 4.

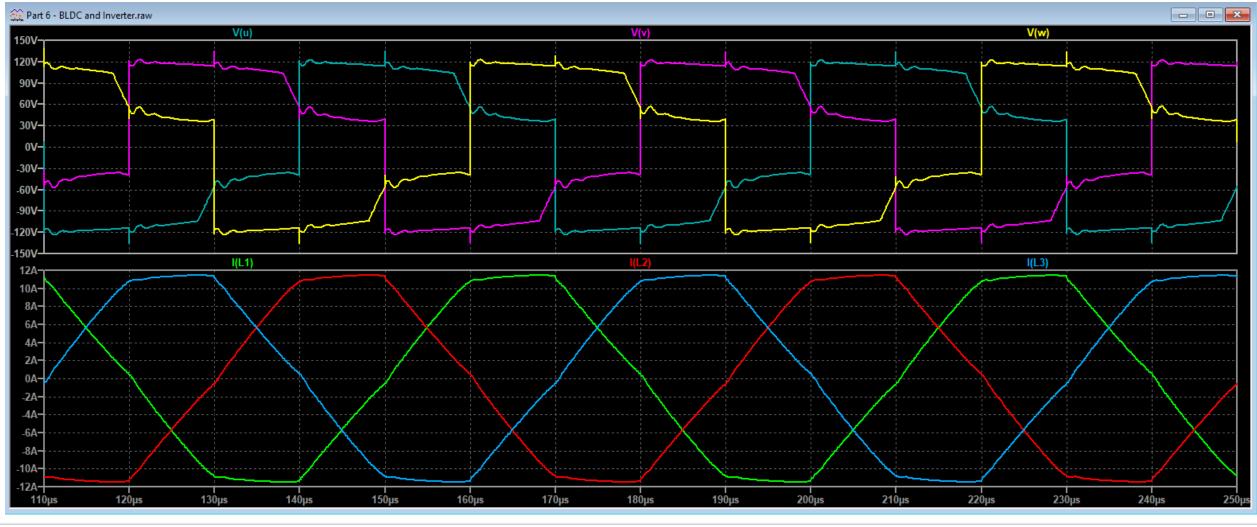

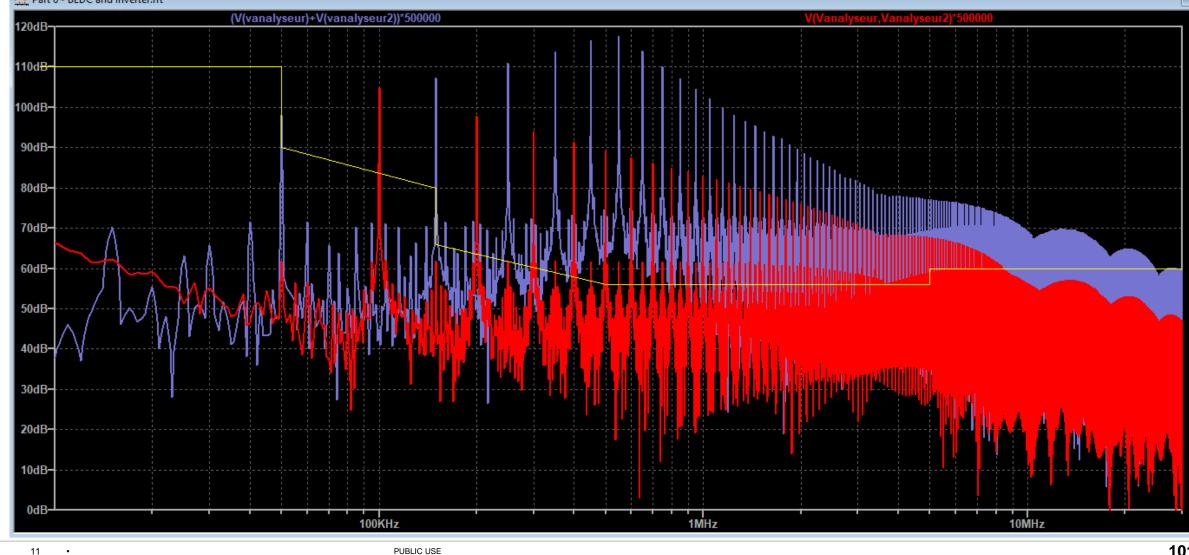

- Brushless DC motor and inverter Using ".STEP" and ".PARAM" 5.

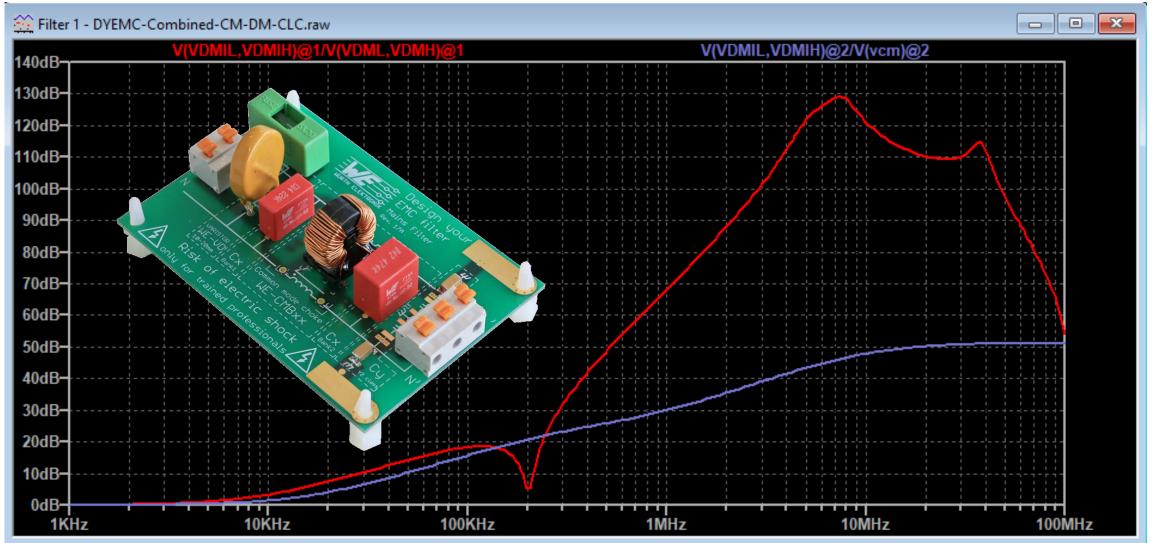

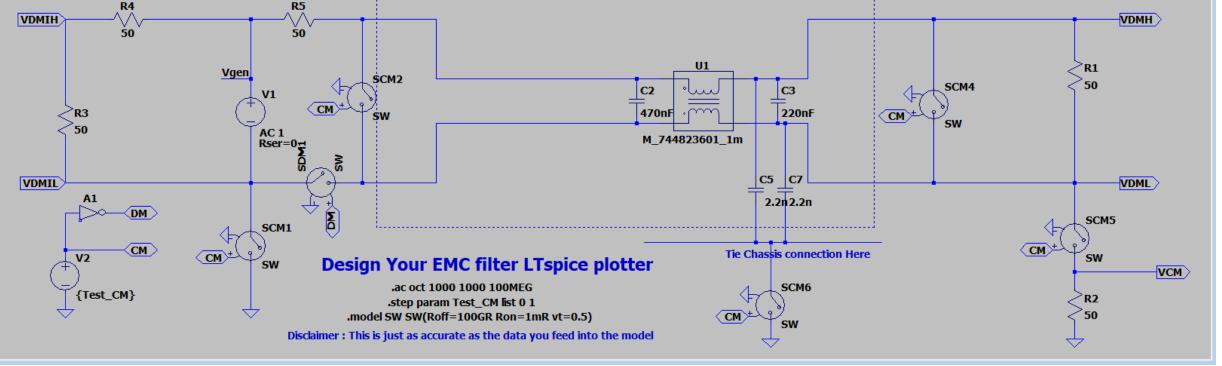

- Evaluation of filter response "@" Plot directives and Boolean Enabled sources 6.

- Power Factor and Harmonic current (IEC 61000-3-2) 7.

- 8. Surges according to IEC 61000-4-5 and ISO 7637-2

#### Setup Getting the tools ready

https://www.analog.com/en/design-center/design-tools-and-calculators/ltspice-simulator.html

https://www.we-online.com/redexpert

more than you expect

WÜRTH F

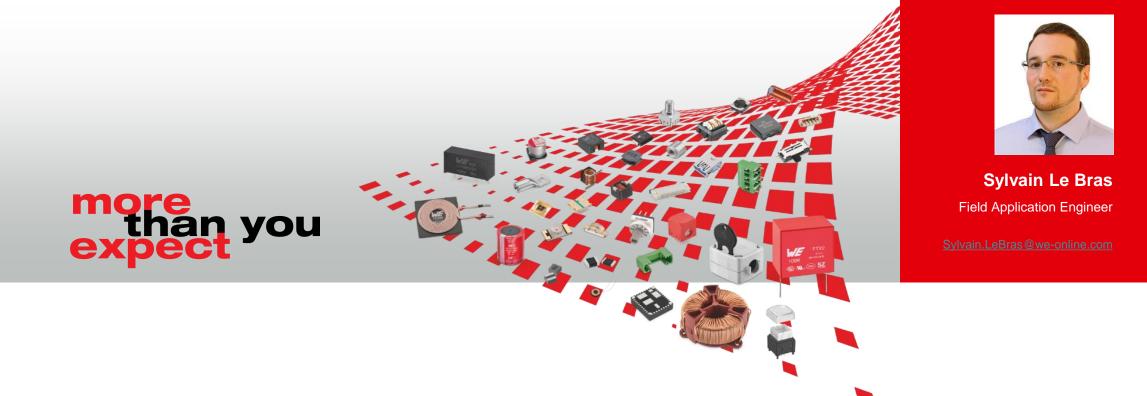

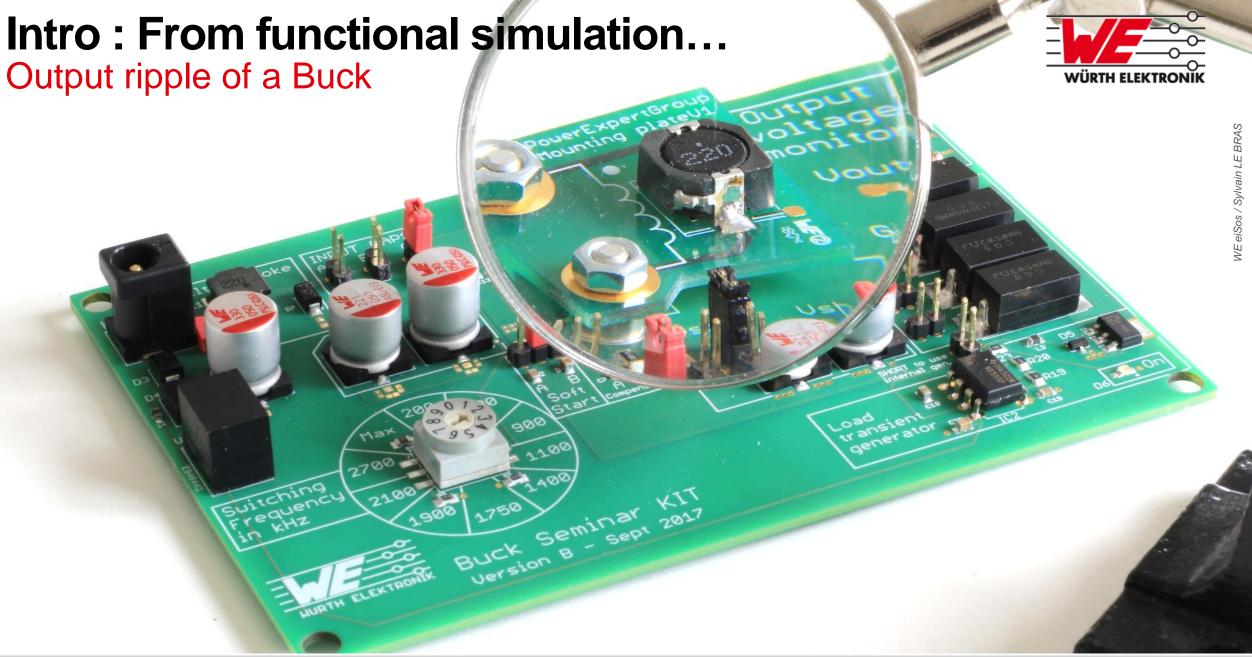

# Intro : From functional simulation...

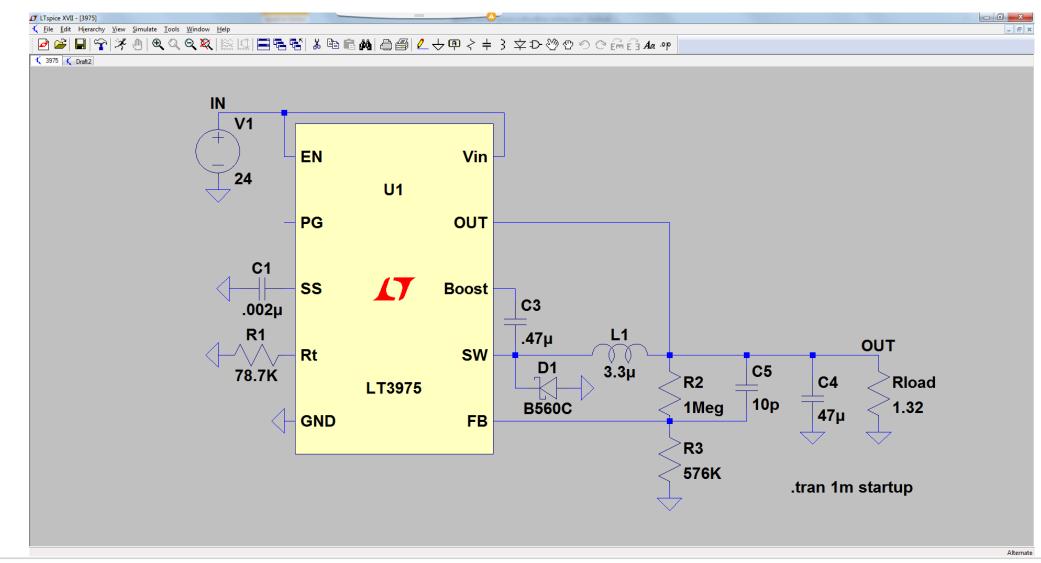

#### Output ripple of a Buck

LTspice XVII - [Draft2]

K \_ Eile Edit Hierarchy ⊻iew Simulate Tools Window Help

🕻 3975 🕻 Draft2

FB o

GND

WÜRTH ELE

# Intro : From functional simulation...

#### Output ripple of a Buck (without the "hardcore mathematics")

٠

#### Output ripple of a Buck Hardcore maths ?

# $V = R \cdot I$ $\Delta V = Z_C \cdot \Delta I_L$

WÜRTH ELEKTRONI

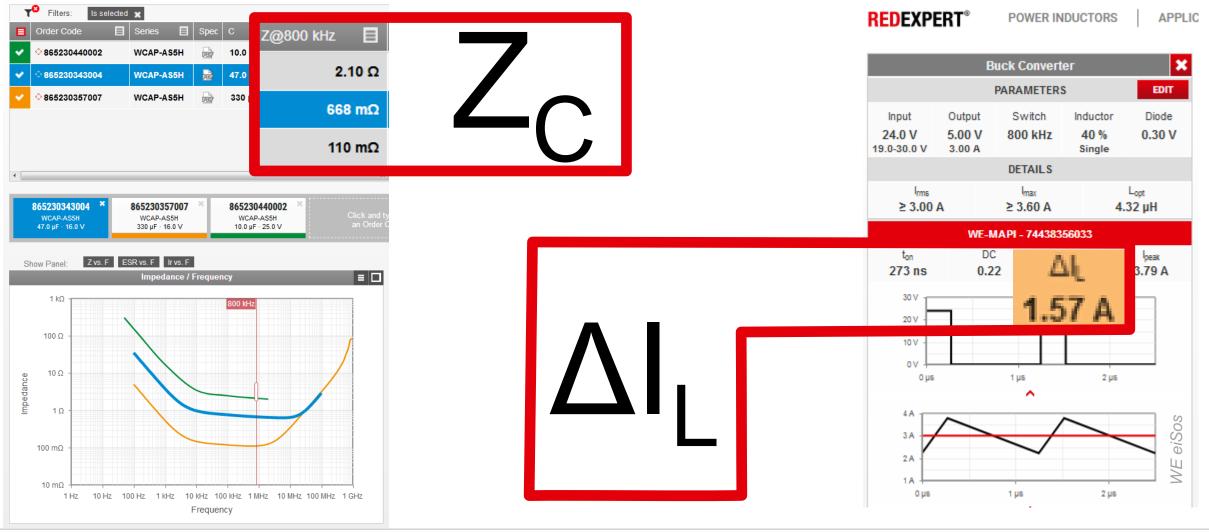

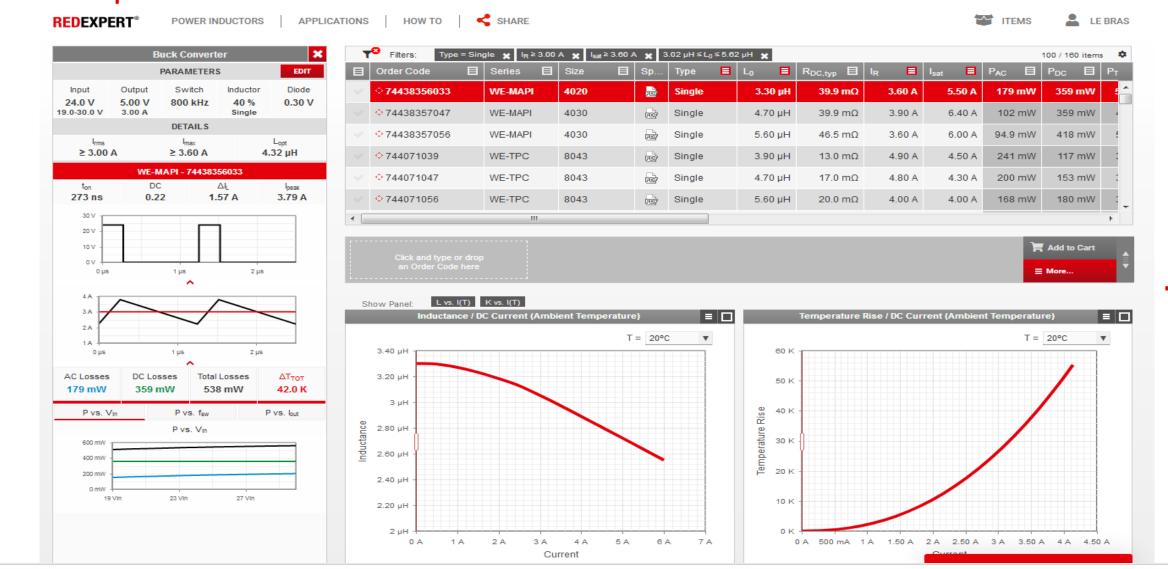

#### **Output ripple of a Buck** Redexpert : an ode to laziness

**REDEXPERT**<sup>®</sup> ALUMINIUM ELECTROLYTIC CAPACITORS APPLICATIONS

2020 May 11

•

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

WÜR'

#### Output ripple of a Buck Redexpert : an ode to laziness

#### Output ripple of a Buck Redexpert : an ode to laziness

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

PUBLIC USE

2020

May

11

•

Link

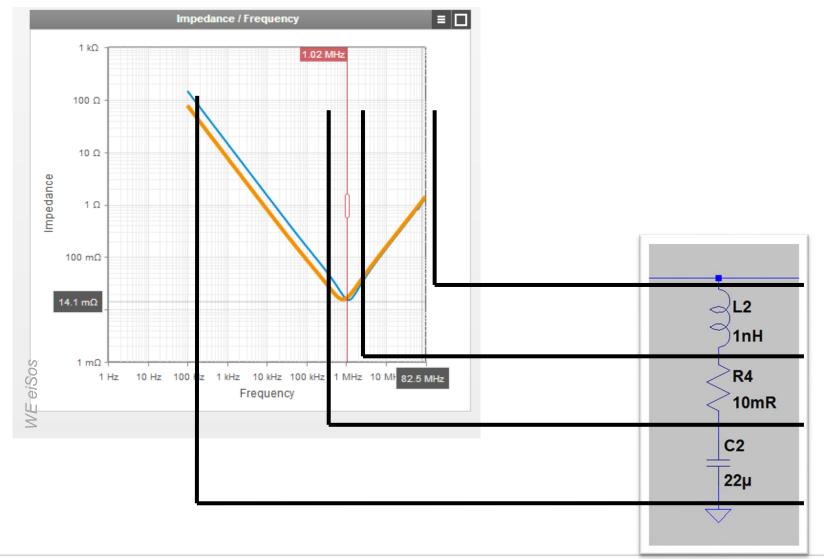

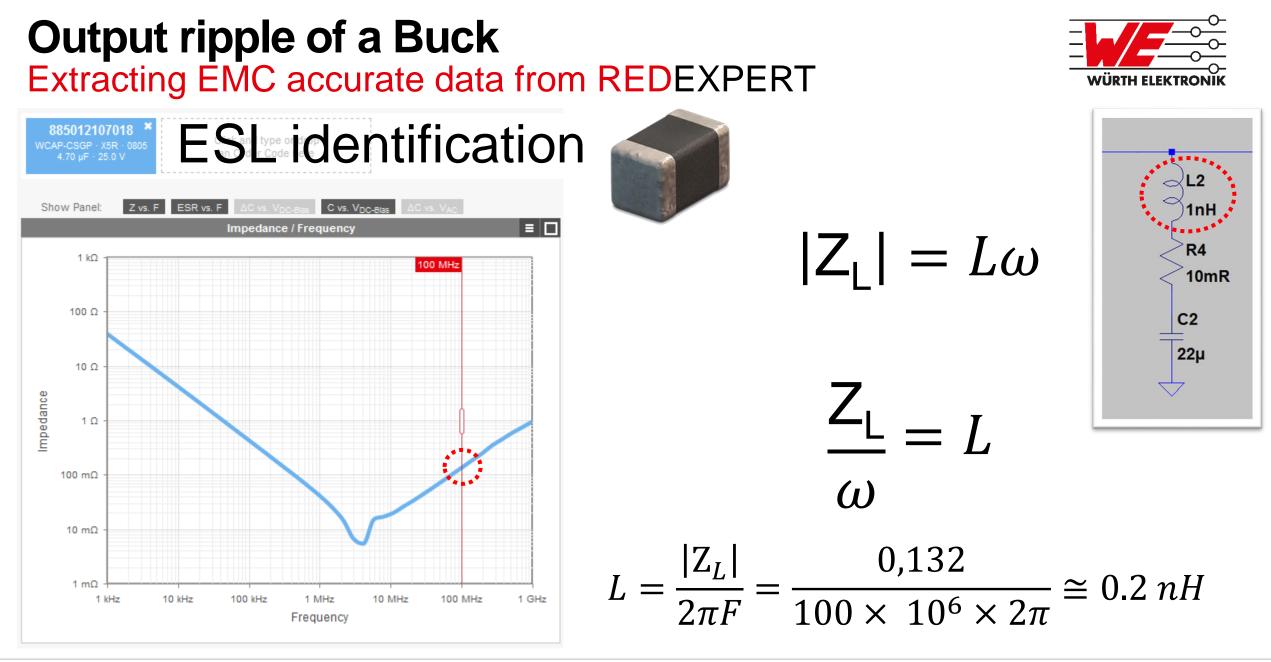

### Output ripple of a Buck Extracting EMC accurate data from REDEXPERT

•

#### **Output ripple of a Buck** Extracting EMC accurate data from REDEXPERT 890273427005CS **ESL** identification WCAP-FTBE · 27.5 mm 4.70 µF · 250 V Z vs. F ESR vs. F VRMS vs F Show Panel Impedance / Frequency 🐼 🔊 🞯 SZ **R4** $|\mathsf{Z}_{\mathsf{I}}| = L\omega$ 10mR 1 kΩ **C2** 100 Ω 22µ mpedance 10 Ω 1Ω (1)100 mΩ $=\frac{5}{100\times\,10^6\times2\pi}\cong 8\,nH$ 1 kHz 10 kHz 1 MHz 100 kHz 10 MHz 100 MHz Frequency

2020 May 11

-23

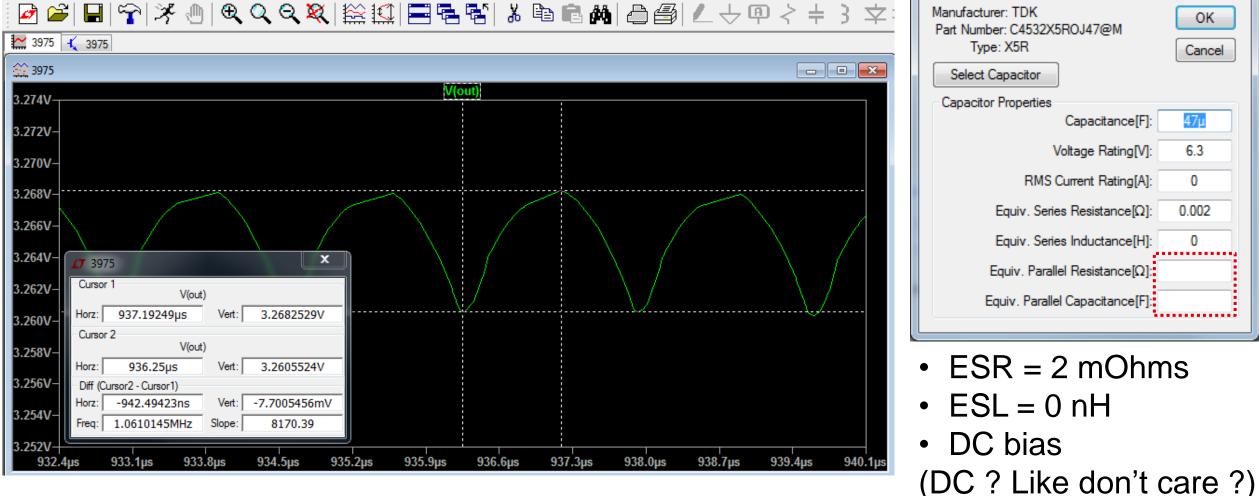

# Output ripple of a Buck Example of (non) EMC accurate impact on simulation

2020 May 11

## Output ripple of a Buck Example of (non) EMC accurate impact on simulation

2020 May 11

PUBLIC USE

WÜRTH

V(vcap

866.4us

867.2us

WE eiSos

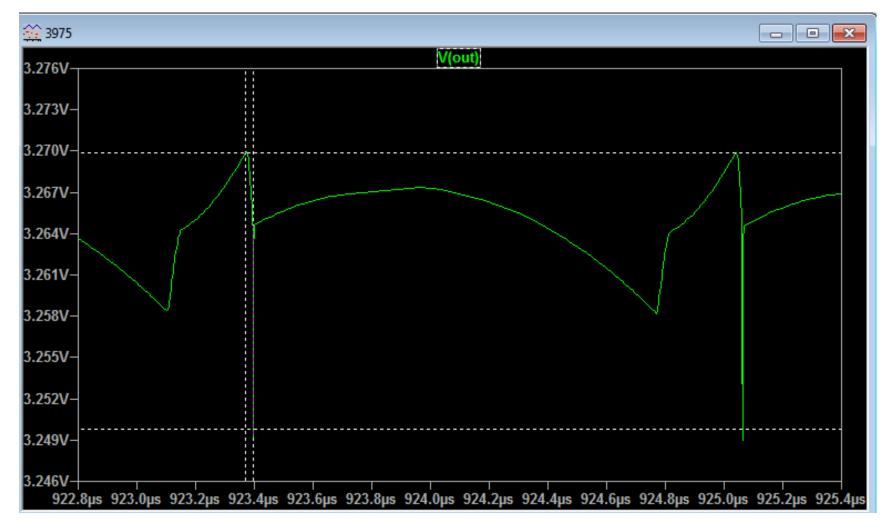

# Output ripple of a Buck

Example of EMC accurate simulation

Charge and discharge of cap

2020

May

11

PUBLIC USE

3.280V-3.278V-

3.276V 3.274V 3.272V 3.272V 3.270V

3.268V

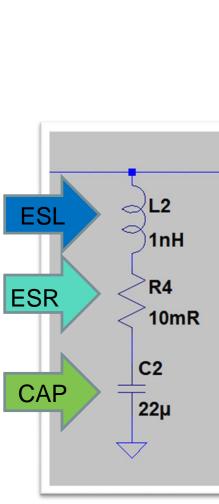

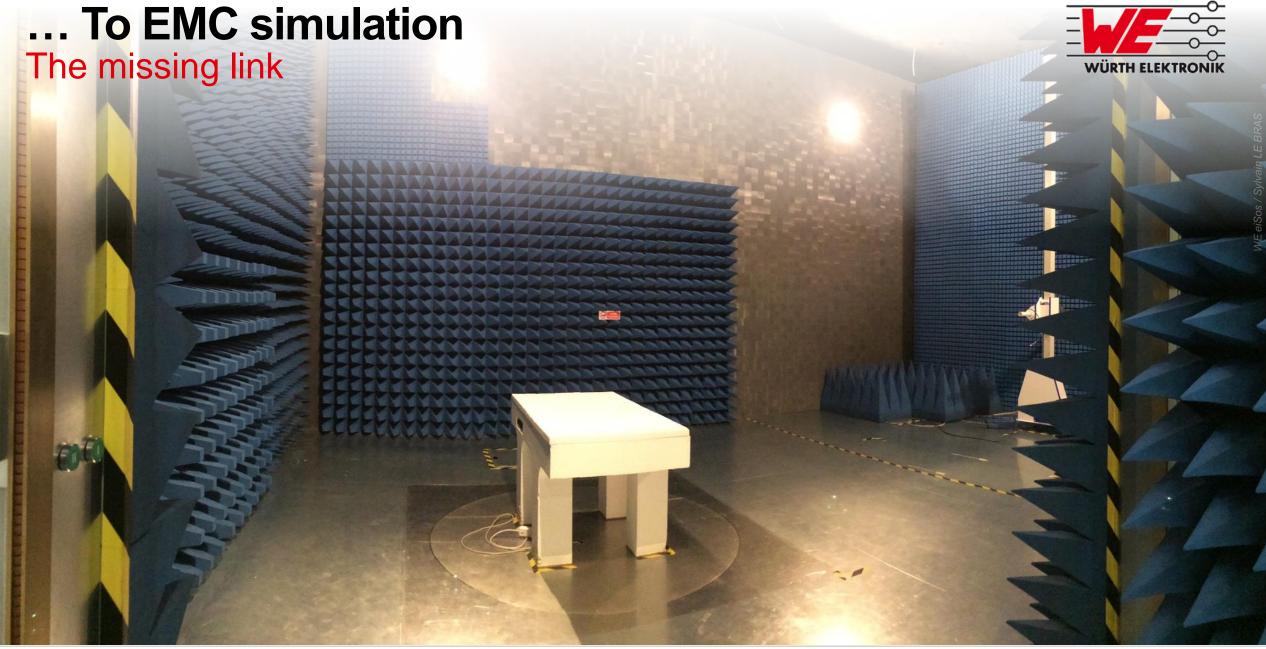

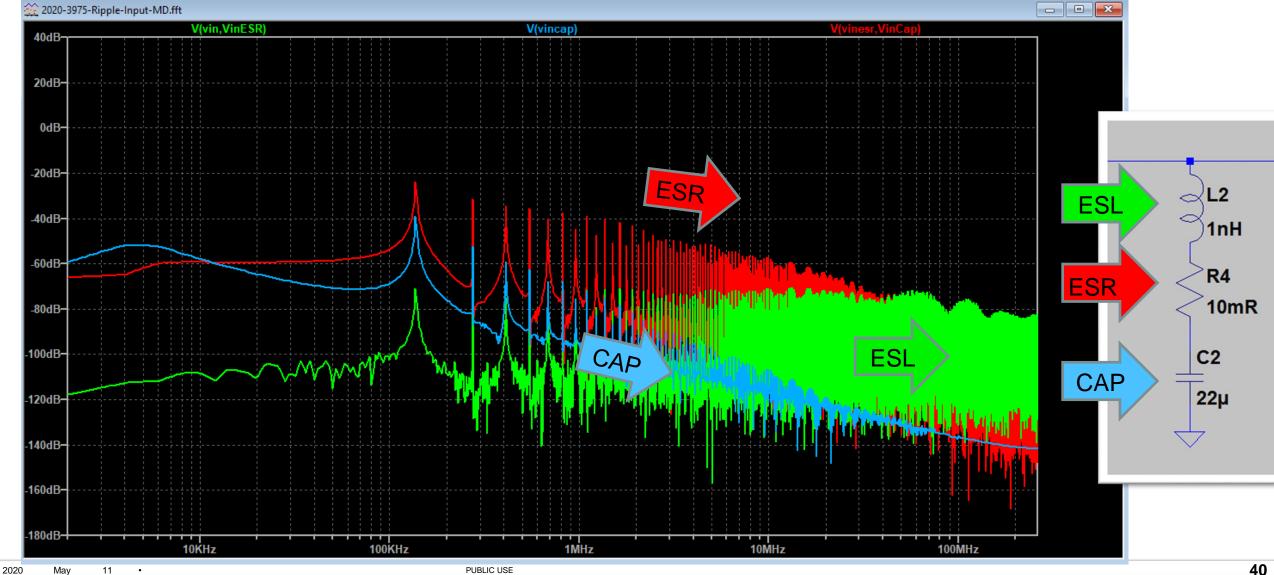

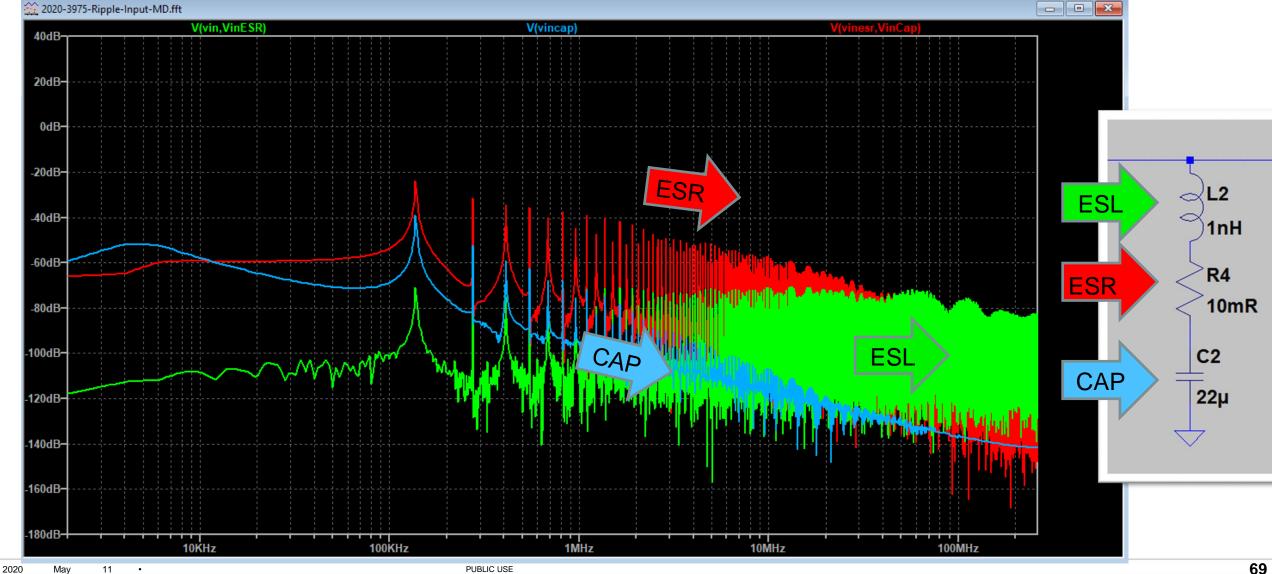

#### Capacitor ripple voltage example ESR / ESL / CAP breakdown in frequency

PUBLIC USE

2020

11

May

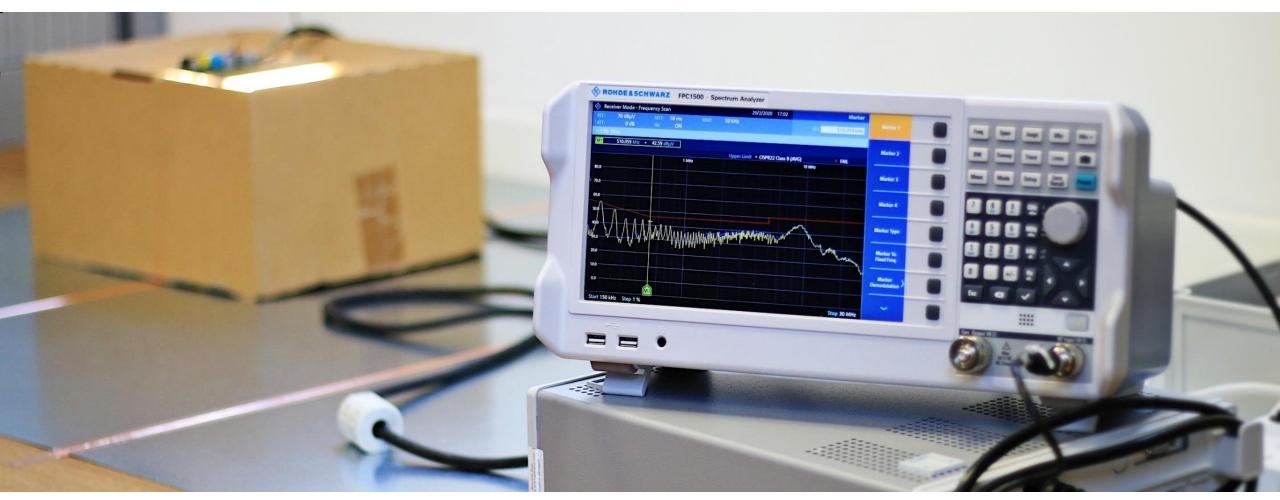

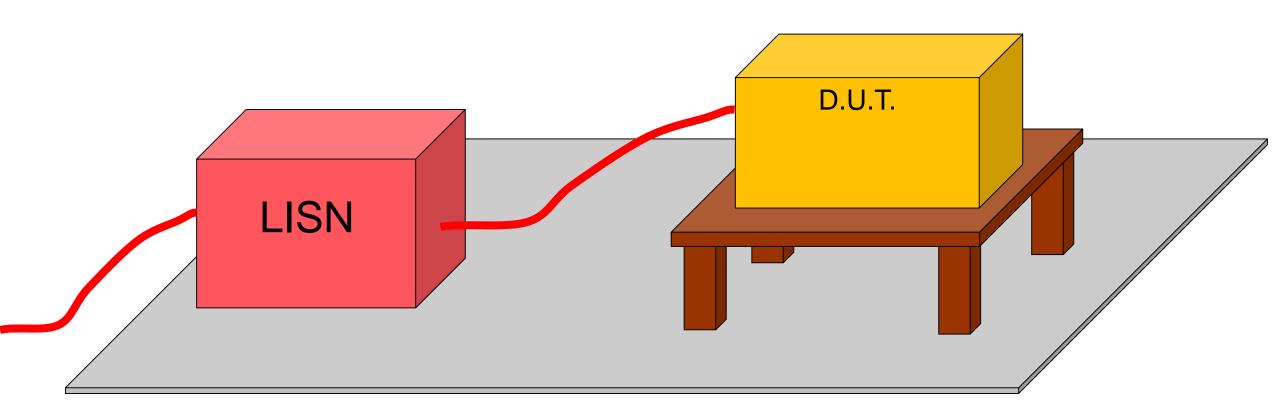

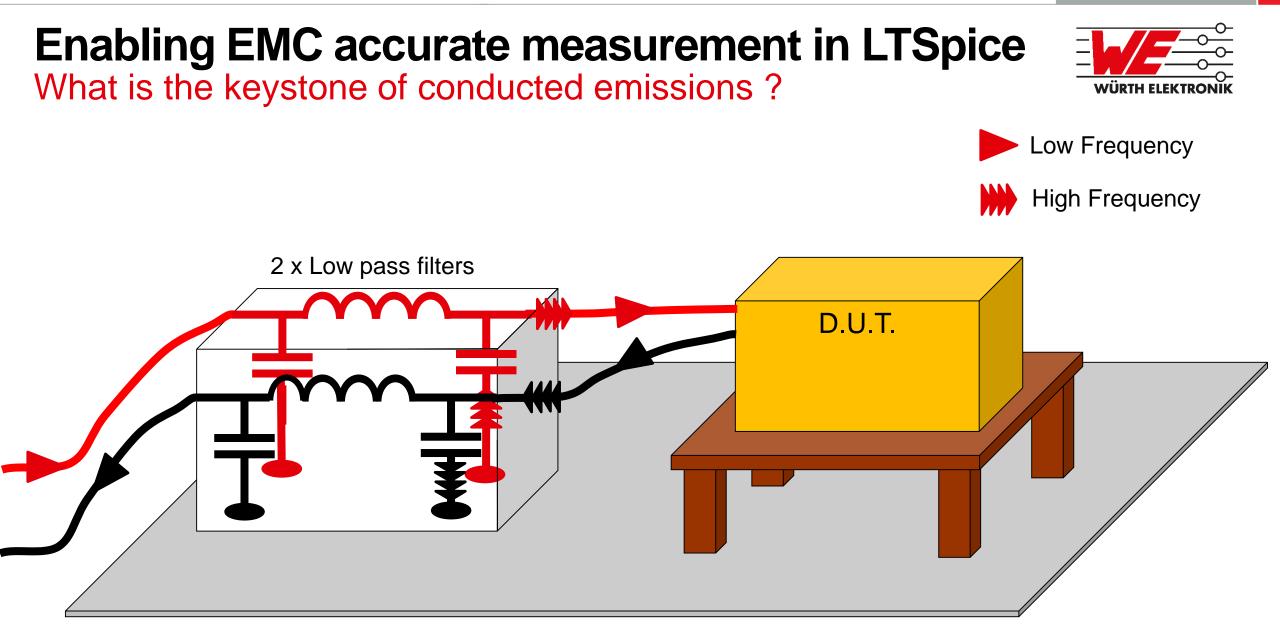

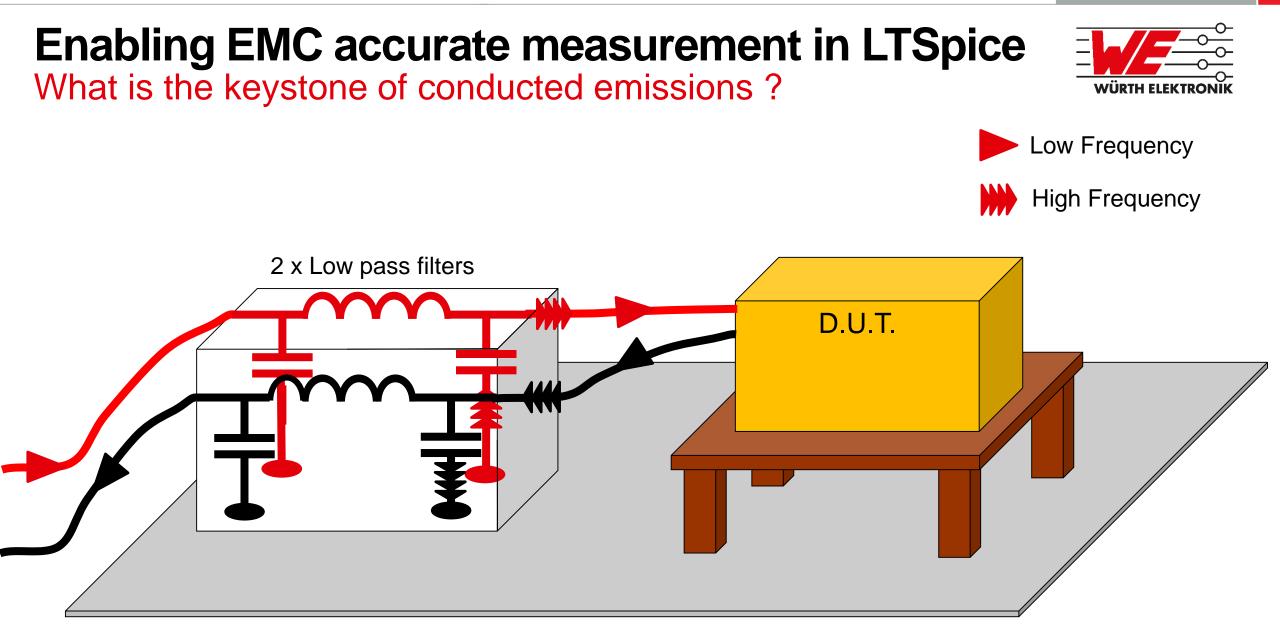

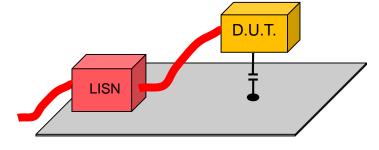

#### Enabling EMC accurate measurement in LTSpice What is the keystone of conducted emissions ?

2020 May 11

#### Enabling EMC accurate measurement in LTSpice What is the keystone of conducted emissions ?

#### Enabling EMC accurate measurement in LTSpice What is the keystone of conducted emissions ?

2020 May 11

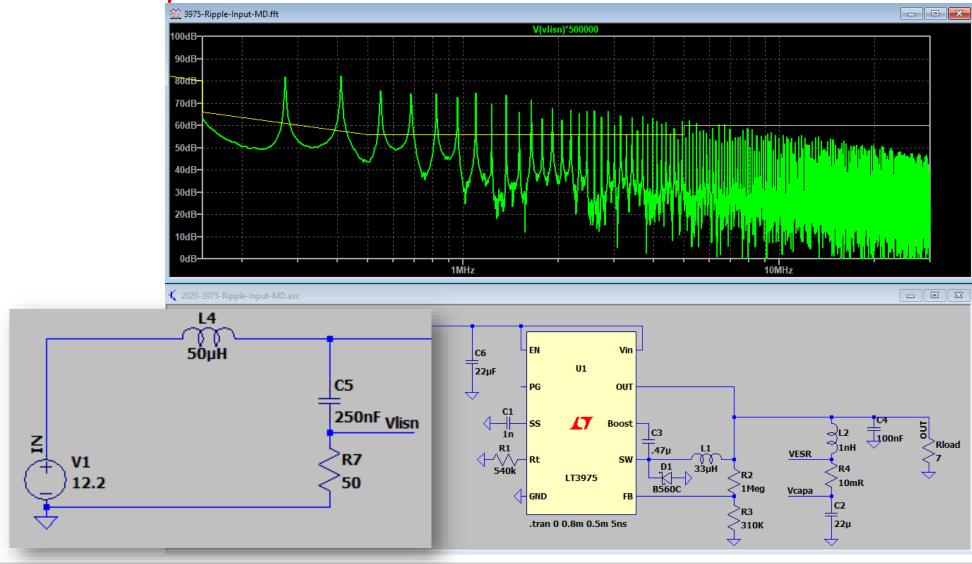

#### Enabling EMC accurate measurement in LTSpice FFT with simplified LISN

2020 May 11

•

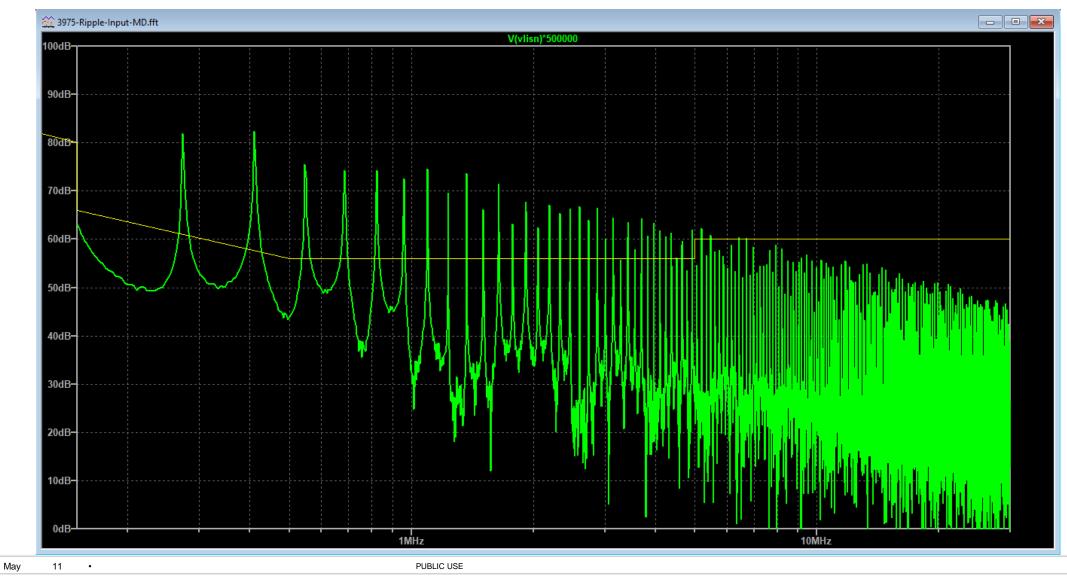

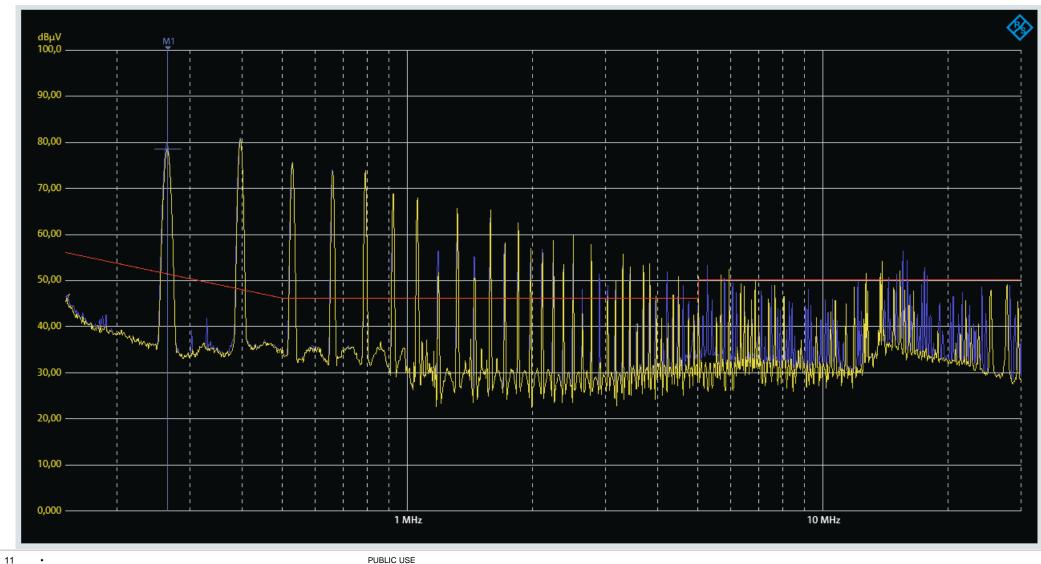

#### **Reality VS Simulation** FFT with simplified LISN

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

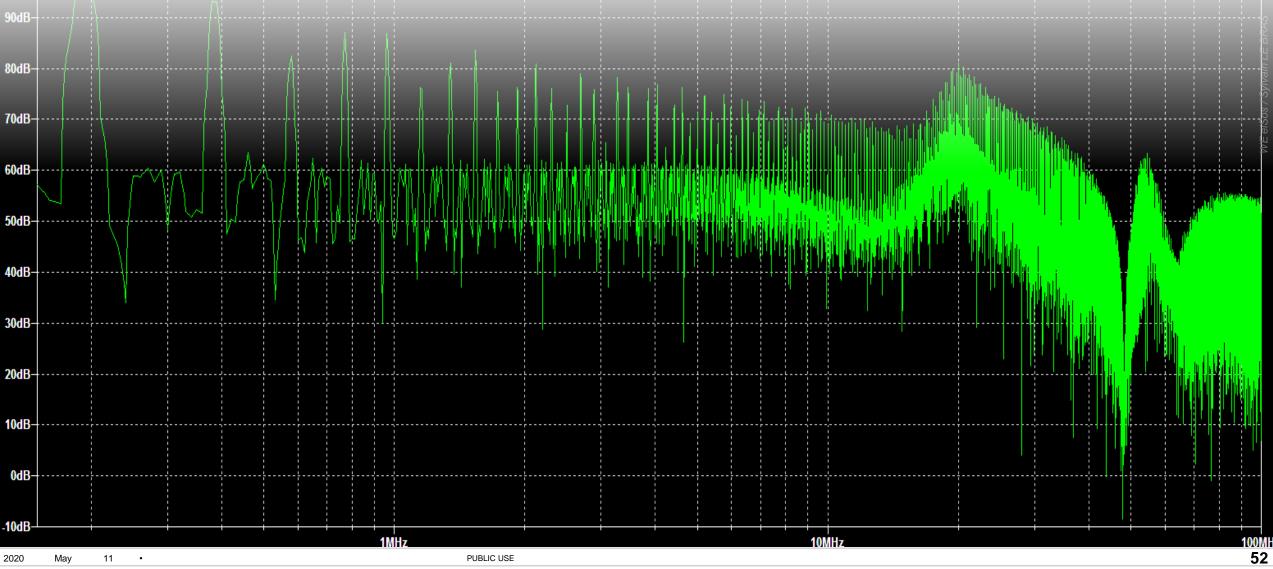

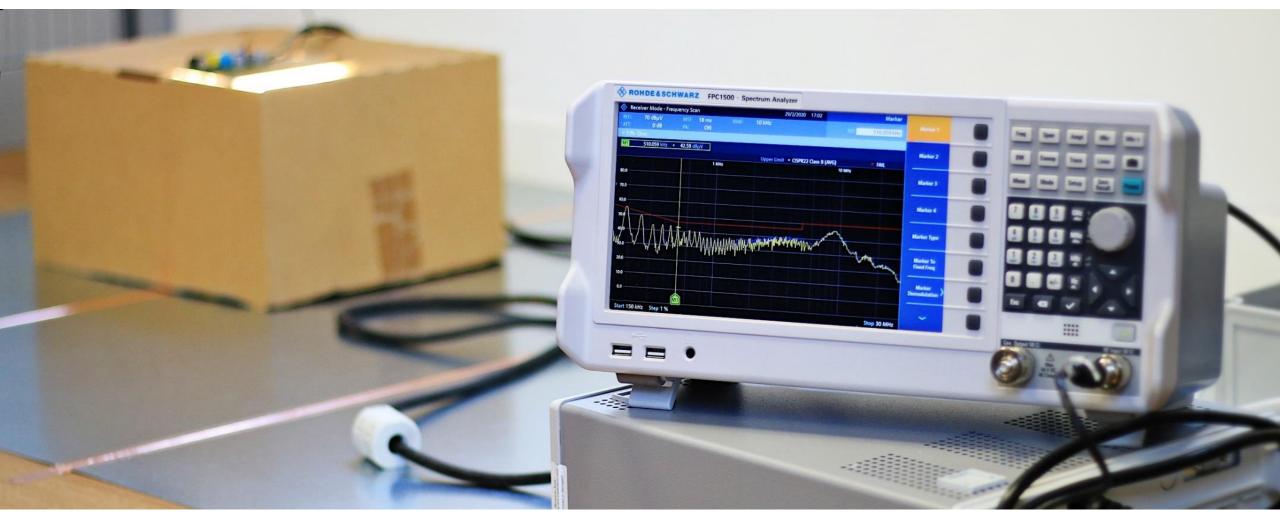

# **Reality VS Simulation**

#### **Conducted Emissions measurement**

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

11

# **Reality VS Simulation**

#### **Conducted Emissions measurement**

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

## Reality VS Simulation ESR / ESL / CAP breakdown in frequency

# **Reality VS Simulation**

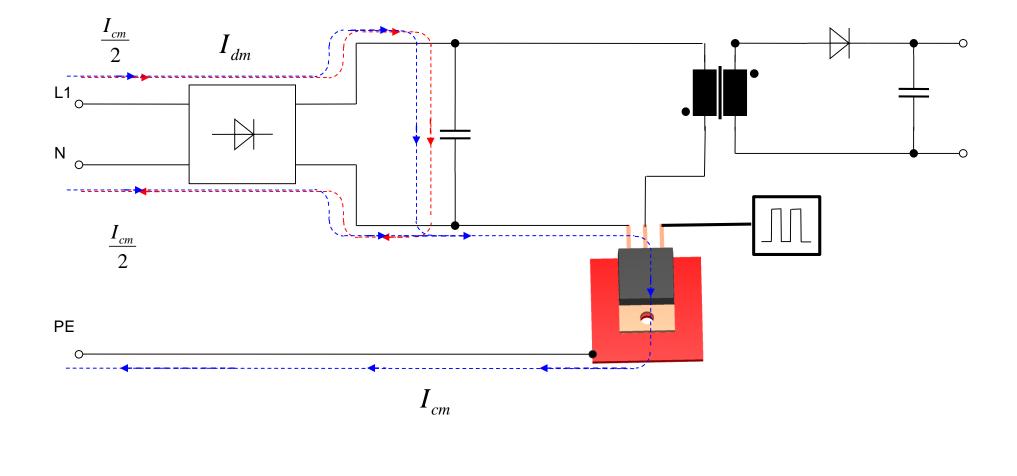

#### EMI measurement = $\sum$ (Common Mode + Differential Mode)

WÜRTH ELEK

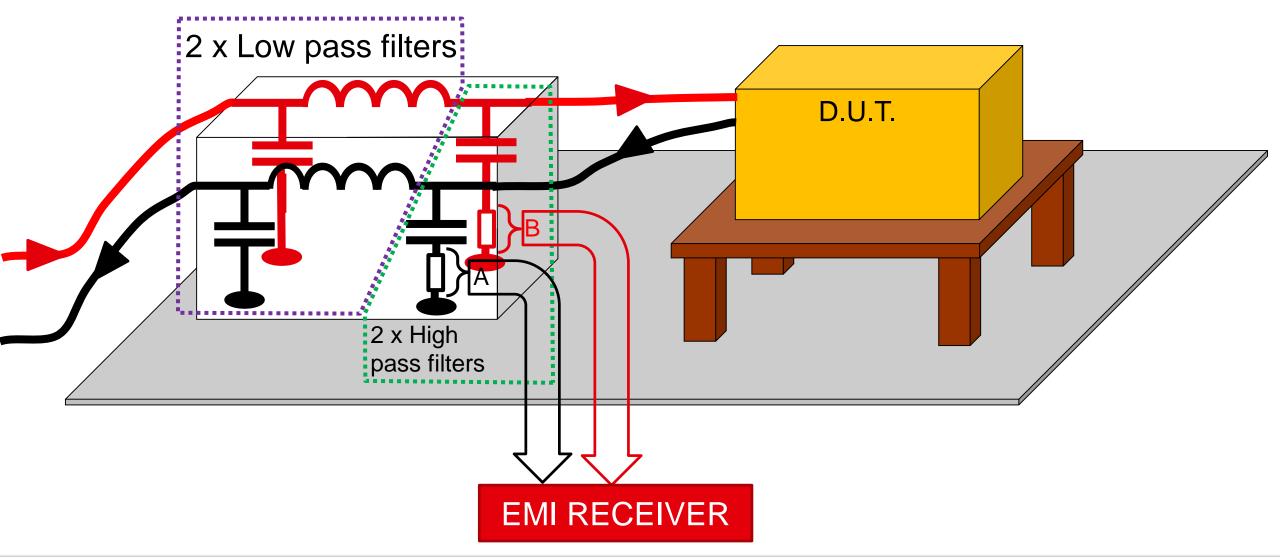

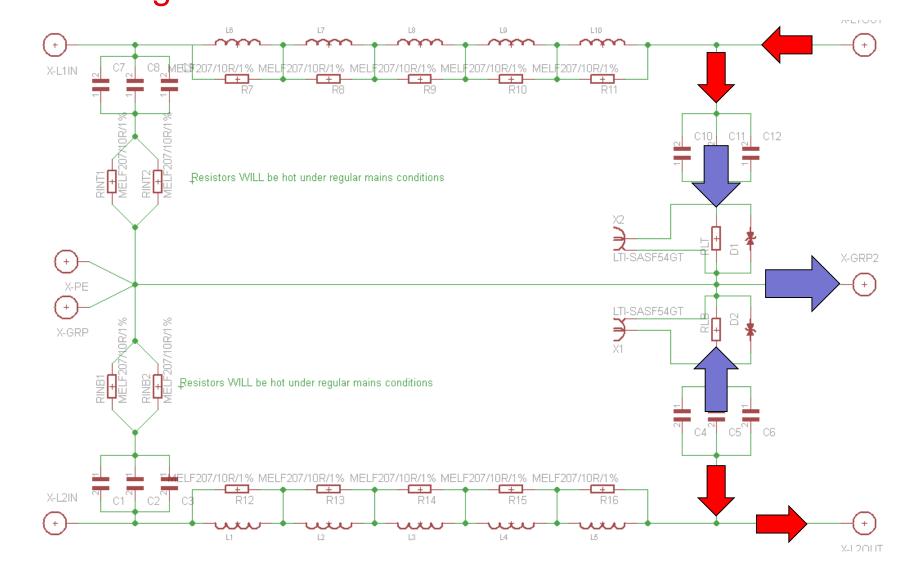

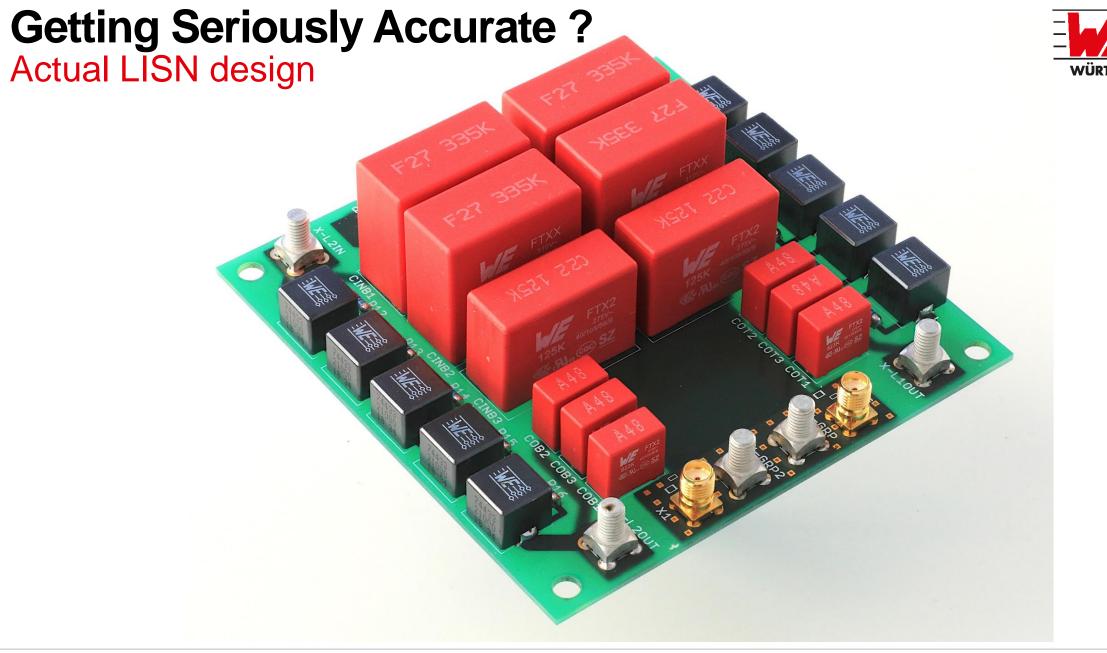

#### Getting Seriously Accurate ? Actual LISN design

2020 May 11

•

•

#### Getting Seriously Accurate ? Simulation Ready LISN design

2020 May 11

•

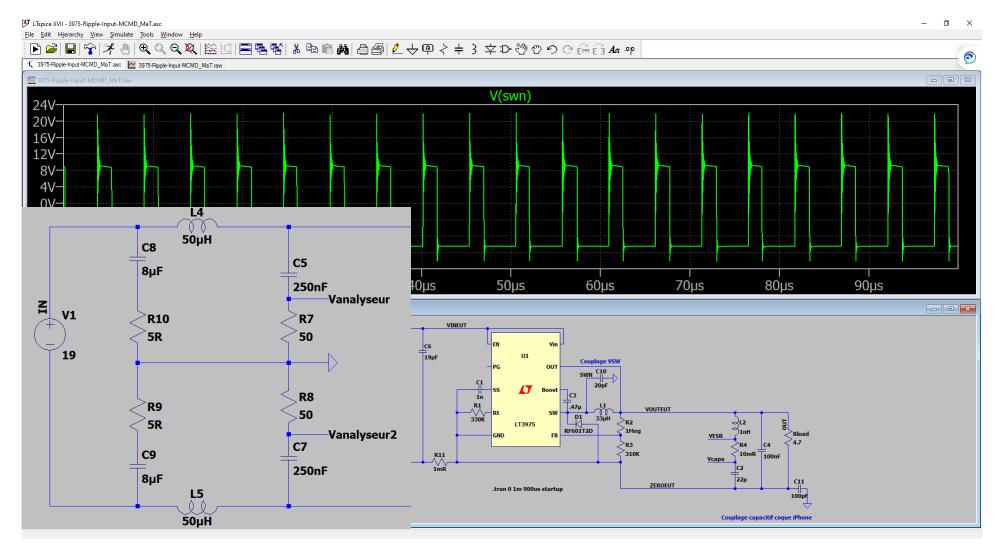

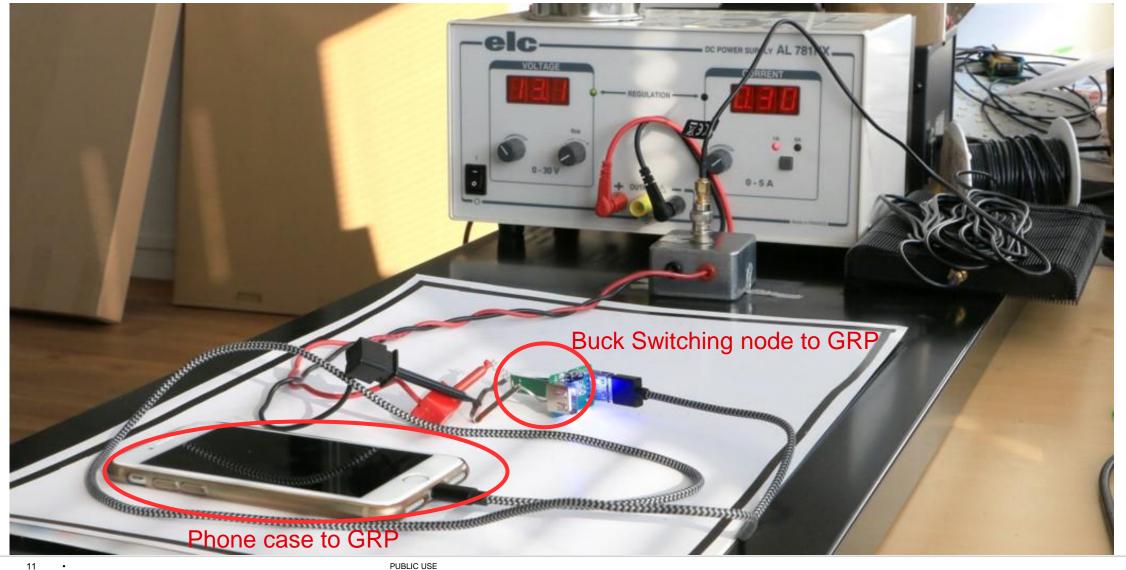

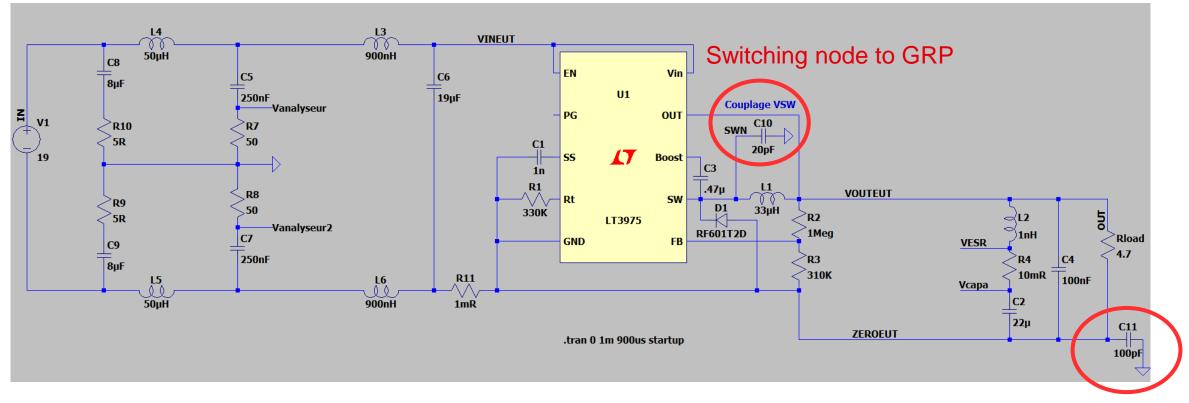

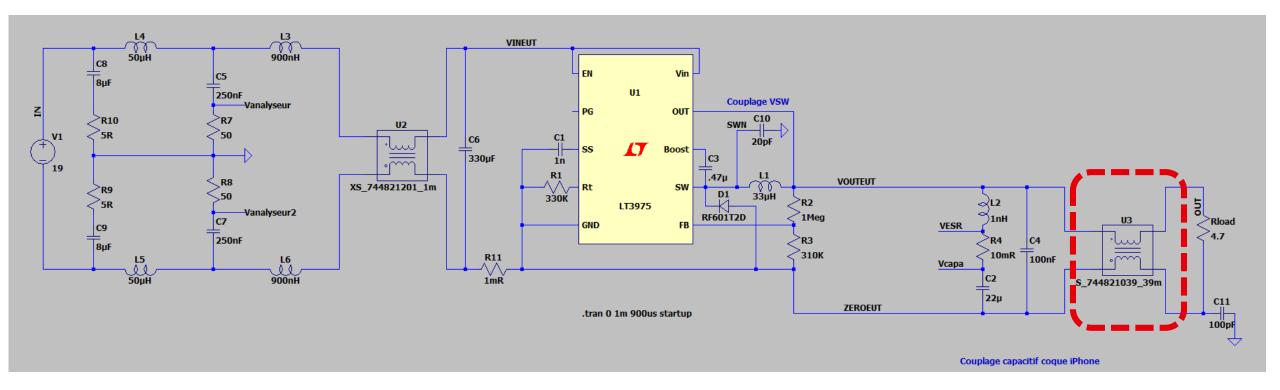

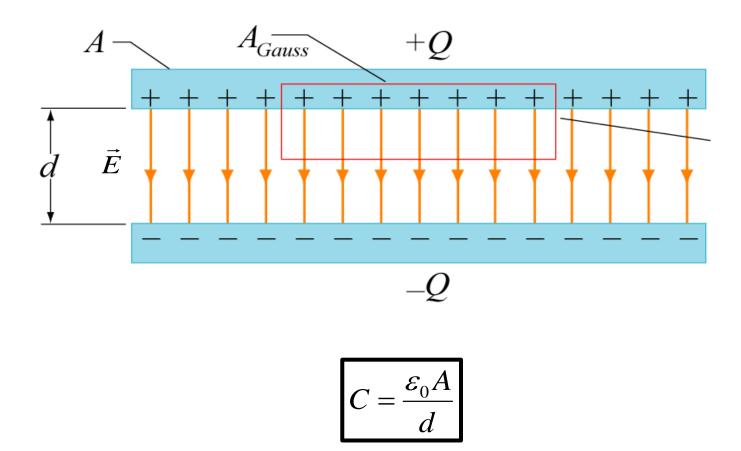

#### Getting Seriously Accurate ? Adding E-Field parasitic coupling

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

#### **Getting Seriously Accurate ?** Adding E-Field parasitic coupling

Phone case to GRP

•

WÜRTH

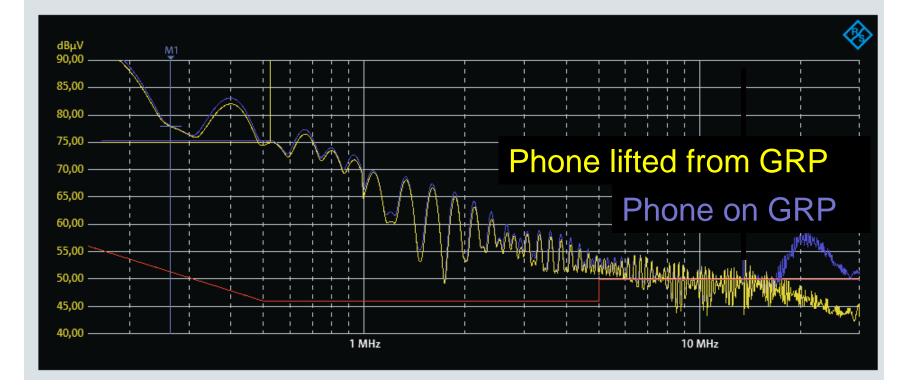

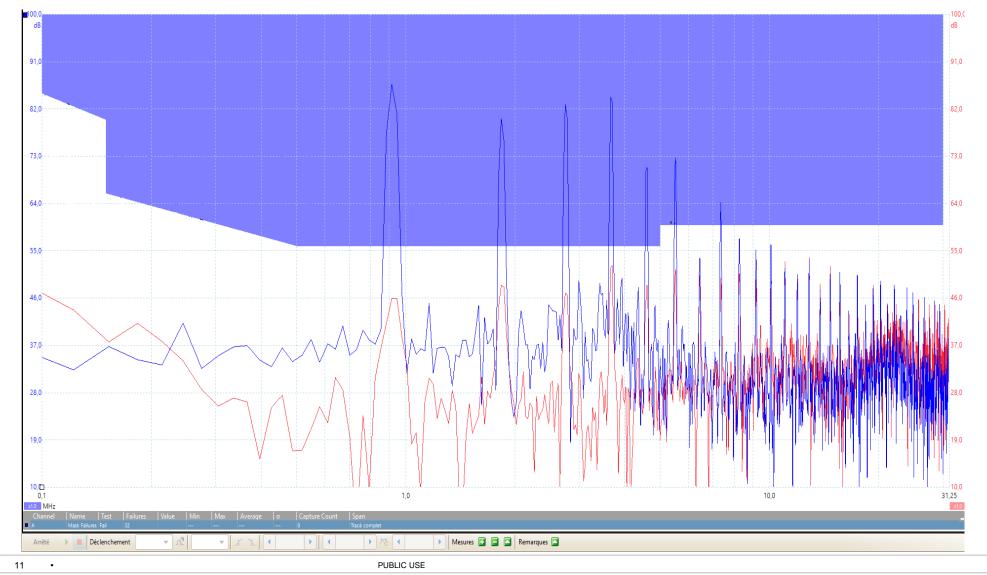

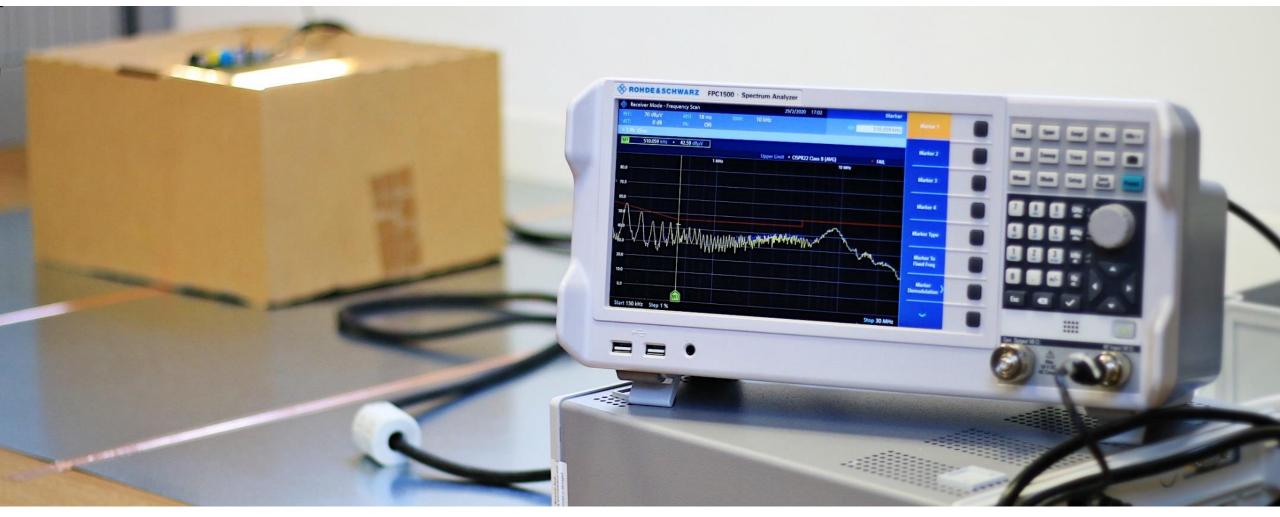

#### Getting Seriously Accurate ? Reality VS Simulation

#### Frequency Scan

Ref Level 80 dBμV RF Attenuator 10 dB RBW 100 kHz Start Frequency 150 kHz Stop Frequency 30 MHz Measurement Time 10 ms Trace Mode Clear / Write Trigger Mode Free Run Trace Detector Average Scan step 0,5 %

•

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

## Getting Seriously Accurate ? Reality VS Simulation

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

#### Getting Seriously Accurate ? Reality VS Simulation

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

11

## Getting Seriously Accurate ? Reality VS Simulation

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

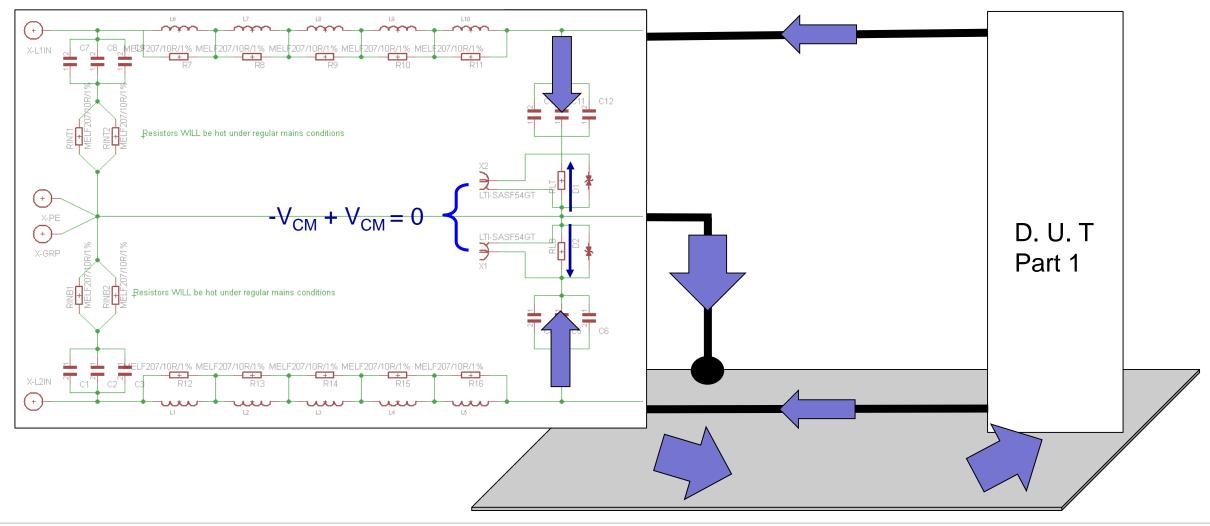

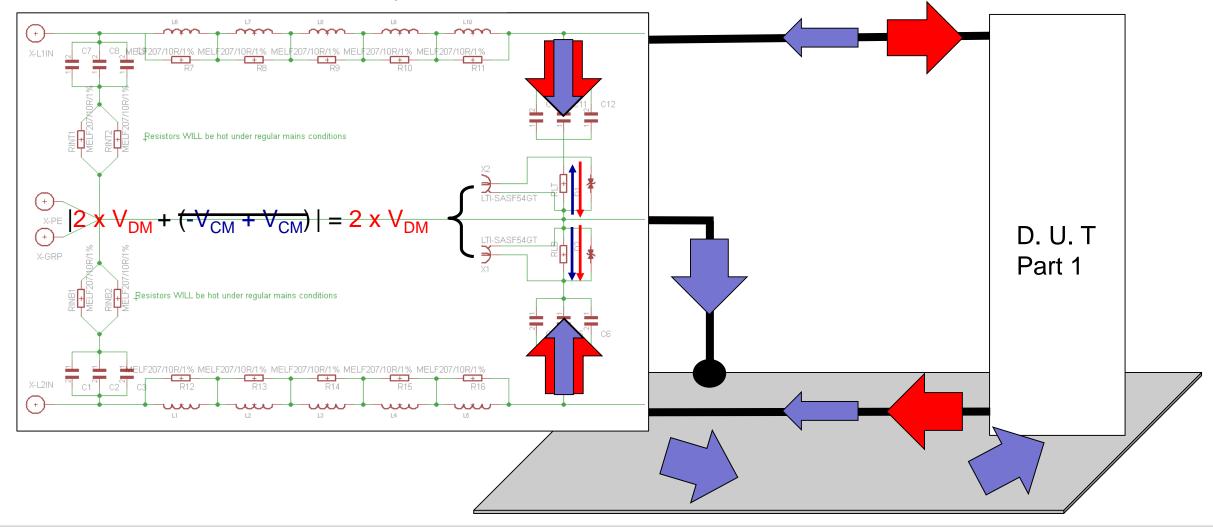

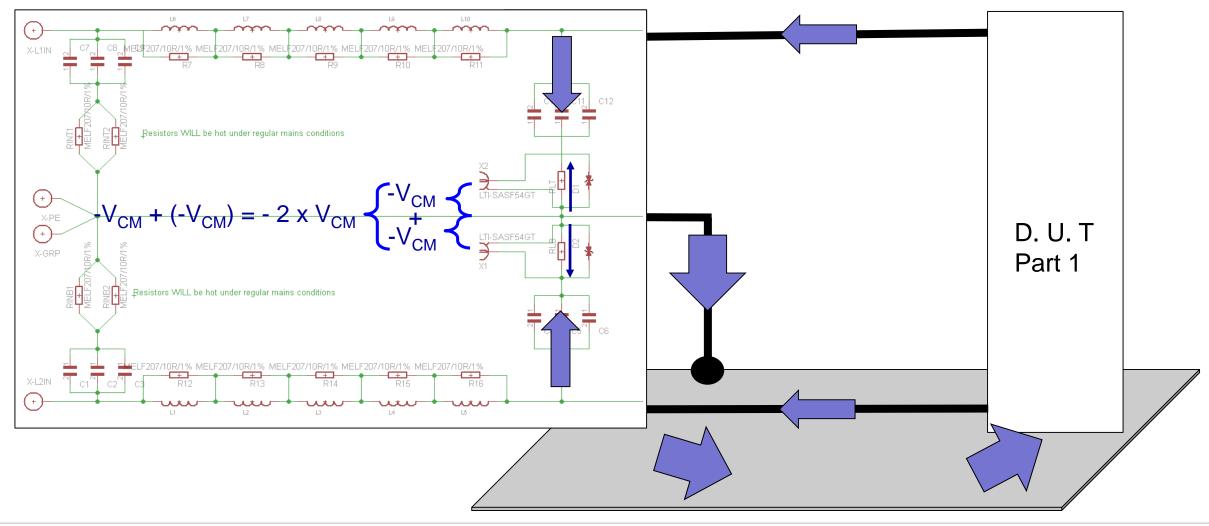

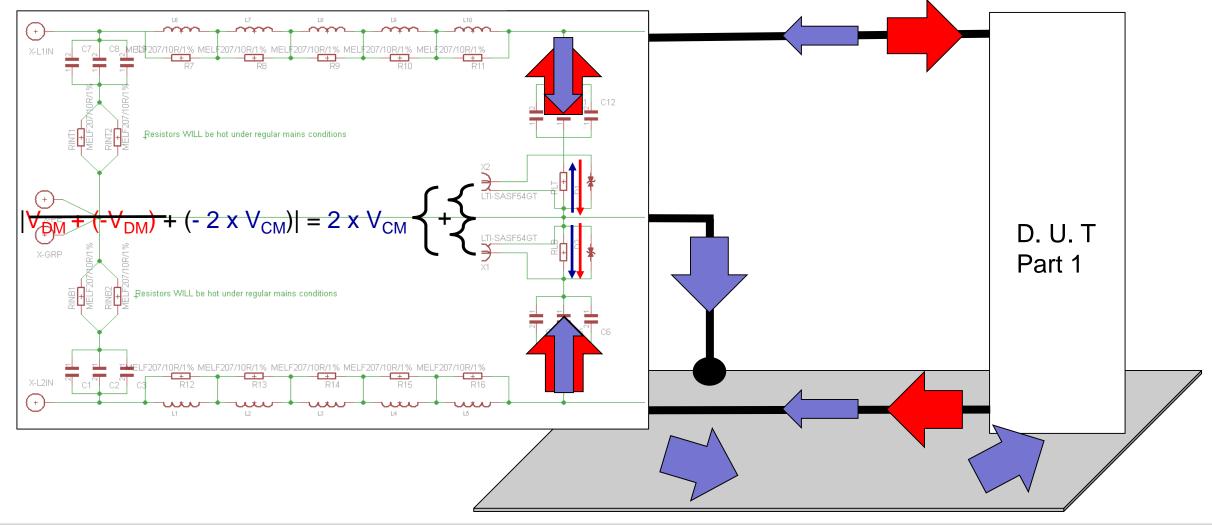

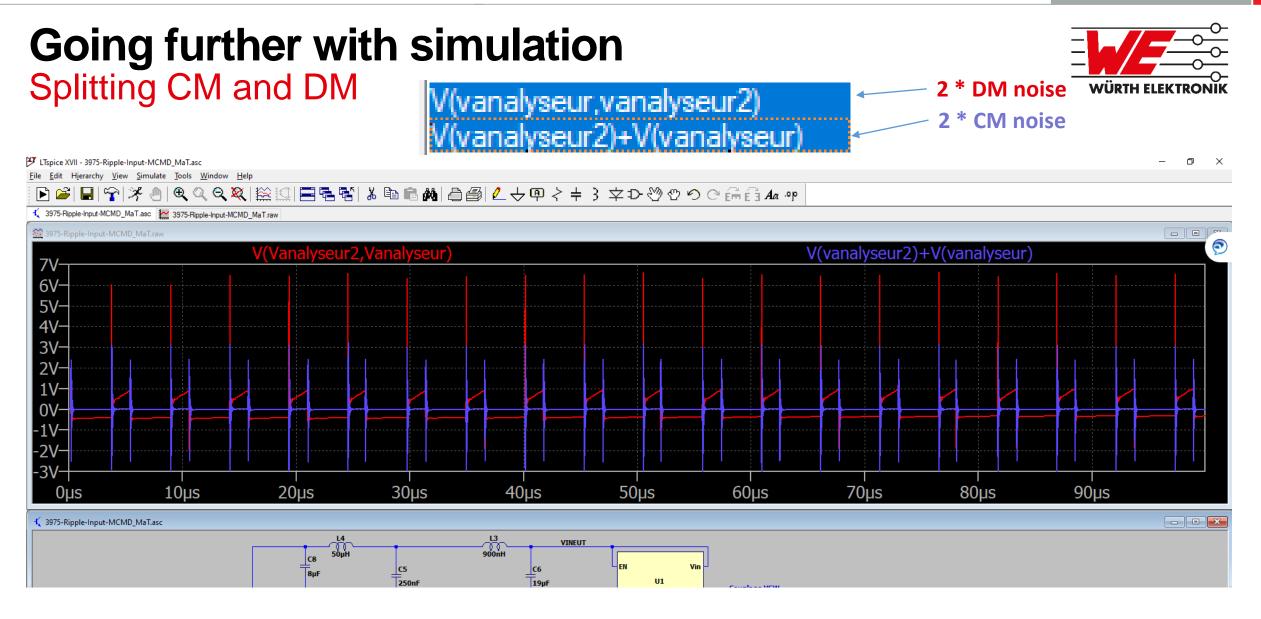

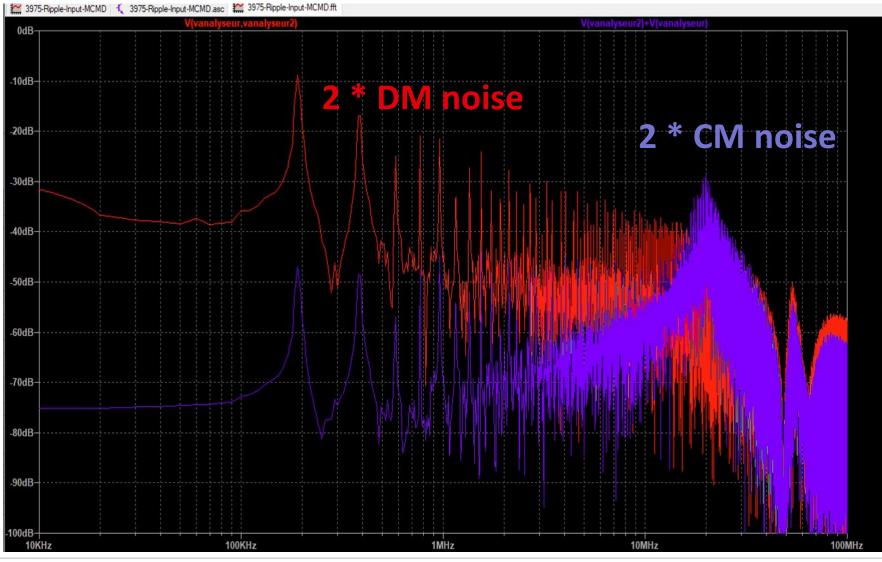

#### Going further with simulation Splitting CM and DM

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

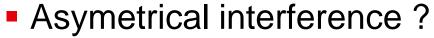

#### Going further with simulation Splitting CM and DM Symetrical interference ? Lß L7 L8 $\sim$ $\sim$ (+)X-L1IN 207/10R/1% MEL ÷ œ, R10 Resistors WILL be hot under regular mains conditions LTI-SASF54GT D. U. T 2 x V X-PE LTI-SASF54G esistors WILL be hot under regular mains conditions? MELF207/10R/1% MELF207/10R/1% MELF207/10R/1% MELF207/10R/1% R14 + R13 + R15 œ + R16 un 1.5 GRP

2020 May 11

•

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

53

WE eiSos / Sylvain LE BRAS

### Going further with simulation Splitting CM and DM

Asymetrical interference ?

٠

PUBLIC USE

### Going further with simulation Splitting CM and DM

2020 May 11

٠

#### **Going further with simulation** Splitting CM and DM Symetrical interference ? Lß L7 L8 $\sim$ $\overline{}$ (+)X-L1IN 207/10R/1% MEL E DE Ð R10 Resistors WILL be hot under regular mains conditions $V_{\rm DM} + (-V_{\rm DM}) = 0 \quad \begin{cases} V_{\rm DM} - V_{\rm DM} - V_{\rm DM} \\ -V_{\rm DM} - V_{\rm DM} \end{cases}$ LTI-SASF54GT D. U. T X-PE Resistors WILL be hot under regular mains conditions F207/10R/1% MELF207/10R/1% MELF207/10R/1% MELF207/10R/1% + R13 R14 œ R16 un GRP

2020 May 11

٠

PUBLIC USE

### Going further with simulation Splitting CM and DM

Asymetrical interference ?

### Going further with simulation Splitting CM and DM

٠

•

#### Going further with simulation Splitting CM and DM

•

PUBLIC USE

#### Going further with simulation Splitting CM and DM

2020 May 11

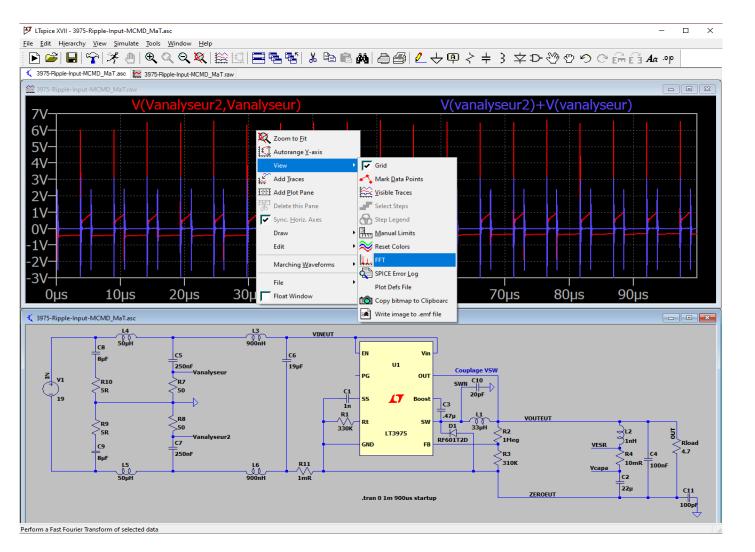

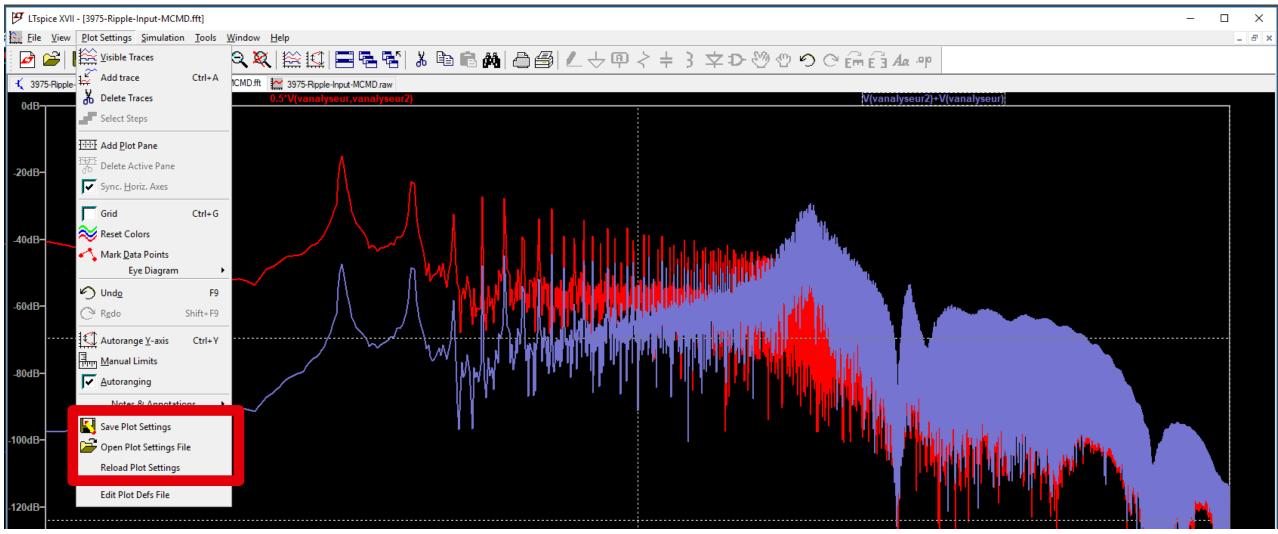

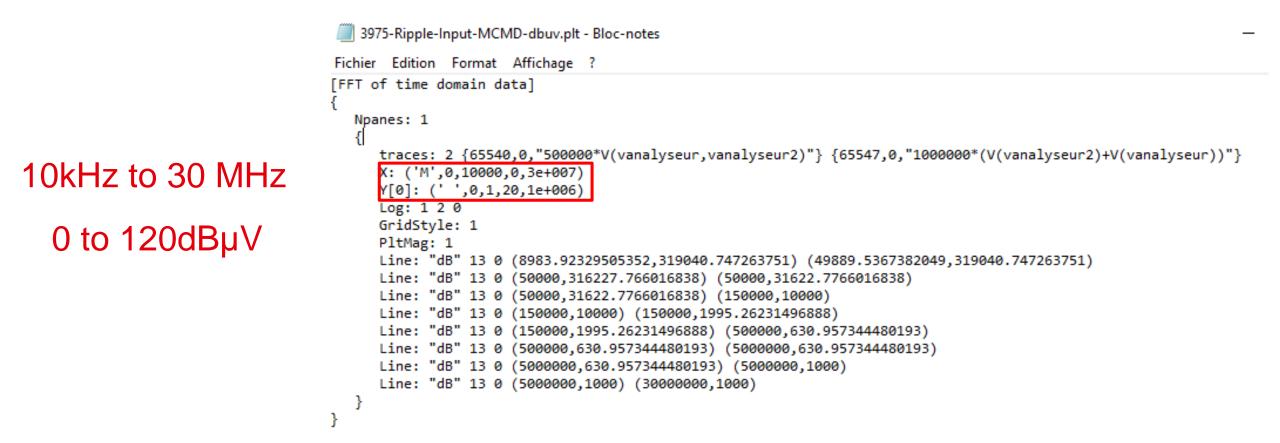

#### Going further with simulation Making simulation look real

→甲Հキ3 字ひ巡巡のひ歸菌ね……

- Scaling to dBµV

- Loading limit lines in LTSpice

- Defining a Frequency range

2020 May 11

ck to edit. Control-Left-Click to integrate

Alternate

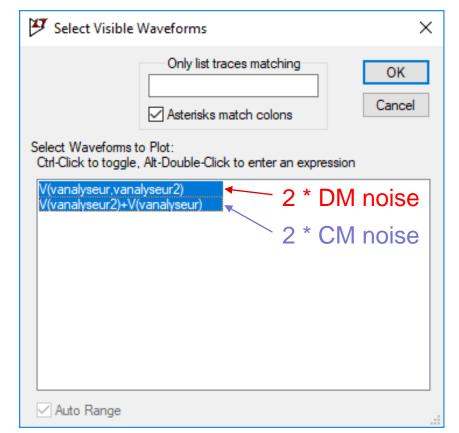

#### Going further with simulation Making simulation look real

| 🎦 Select Visible Waveforms 🛛 🕹 🗙                                                           |  |

|--------------------------------------------------------------------------------------------|--|

| Only list traces matching OK OK Cancel                                                     |  |

| Select Waveforms to Plot:<br>Ctrl-Click to toggle, Alt-Double-Click to enter an expression |  |

| V(vanalyseur,vanalyseur2)<br>V(vanalyseur2)+V(vanalyseur)<br>2 * CM noise<br>2 * CM noise  |  |

| $1 \text{ dBV} = 120 \text{ dB}\mu\text{V}$                                                |  |

| ✓ Auto Range                                                                               |  |

#### Going further with simulation Making simulation look real

2020 May 11

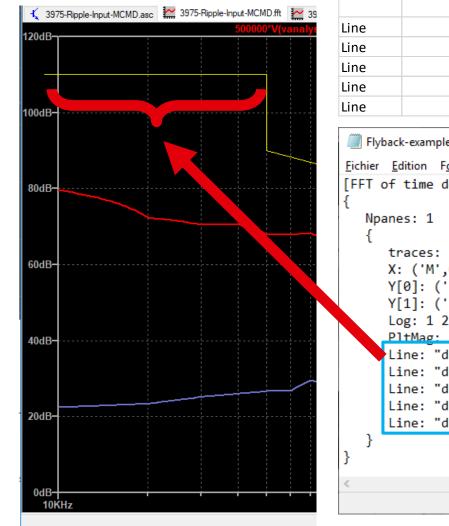

#### **Going further with simulation** Making simulation look real – Adding limit lines

| Start         End         Amp dBμV start         Amp dBμV stop         Line def for LTSPICE           Line         1         9000         50000         110         (900,0.316227766016838) (5000,0)           Line         2         50000         15000         900         (5000,0.0316227766016838) (1500           Line         3         15000         50000         90         666         (5000,0.00199526231496888) (5000,0)           Line         4         50000         500000         50000         50000         56 | •                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Line 2 5000 15000 90 80 (5000,0.0316227766016838) (1500<br>Line 3 15000 50000 66 56 (15000,0.00199526231496888) (50                                                                                                                                                                                                                                                                                                                                                                                                                | •                            |

| Line 3 150000 500000 66 56 (150000,0.00199526231496888) (50                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 00 0 01)                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 100,0.01)                    |

| Line 4 500000 5000000 56 56 (500000,0.000630957344480192) (5                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0000,0.000630957344480192)   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 000000,0.000630957344480192) |

| Line 5 500000 3000000 60 60 (500000,0.001) (3000000,0.001)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                              |

| Flyback-example-2-base - Bloc-notes<br><u>Fichier Edition Format Affichage Aide</u><br>[FFT of time domain data]<br>Npanes: 1                                                                                                                                                                                                                                                                                                                                                                                                      | result • ×                   |

| <pre>{     traces: 1 {2,0, "V(vanalyseur2)+V(vanalyseur)"}     X: ('M',0,9000,0,3000000)     Y[0]: (' ',0,1e-006,10,1)     Y[1]: (' ',0,-200,40,200)     Log: 1 2 0     PltMag: 1     Line: "dB" 4 0 (9000,0.3162277660168) (50000,0.316227766)     Line: "dB" 4 0 (50049.8435712172,0.0317065818612387) (150407.110289202,0.010039778650     Line: "dB" 4 0 (150000,0.00199526231496888) (500000,0.000630957344480192) </pre>                                                                                                     |                              |

| Line: "dB" 4 0 (500000,0.000630957344480192) (5000000,0.000630957344480192)<br>Line: "dB" 4 0 (5000000,0.001) (30000000,0.001)<br>}                                                                                                                                                                                                                                                                                                                                                                                                | ~                            |

| Windows (CRLF) Ln 10, Col 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100% .:                      |

2020 May 11

٠

#### Going further with simulation Making simulation look real – Defining a range

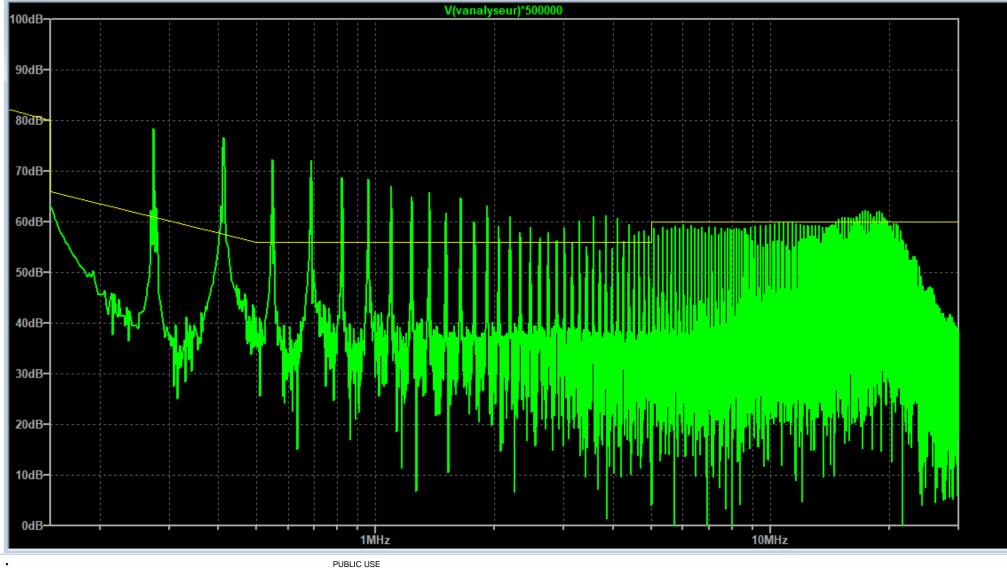

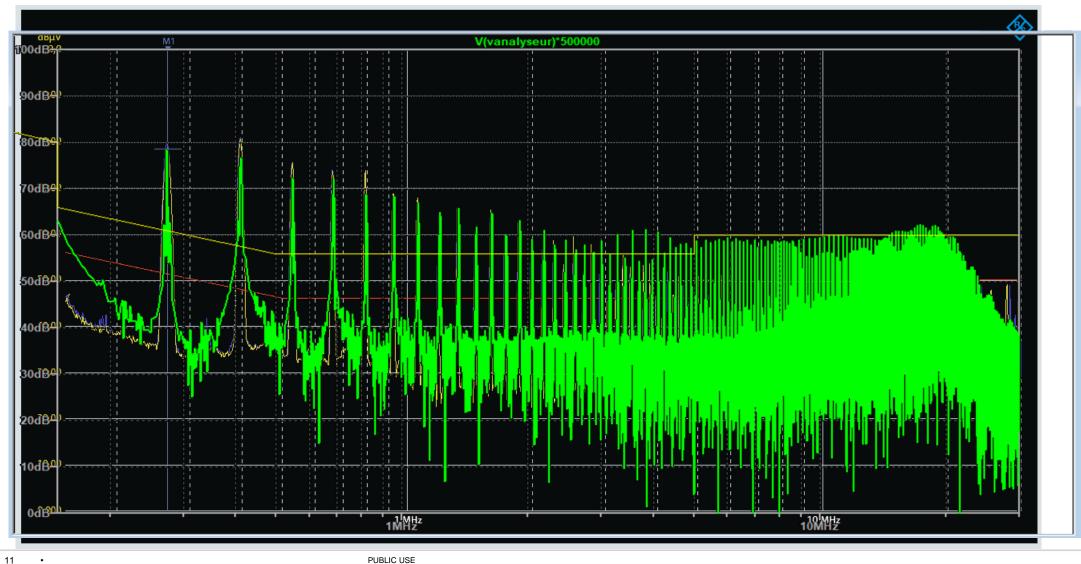

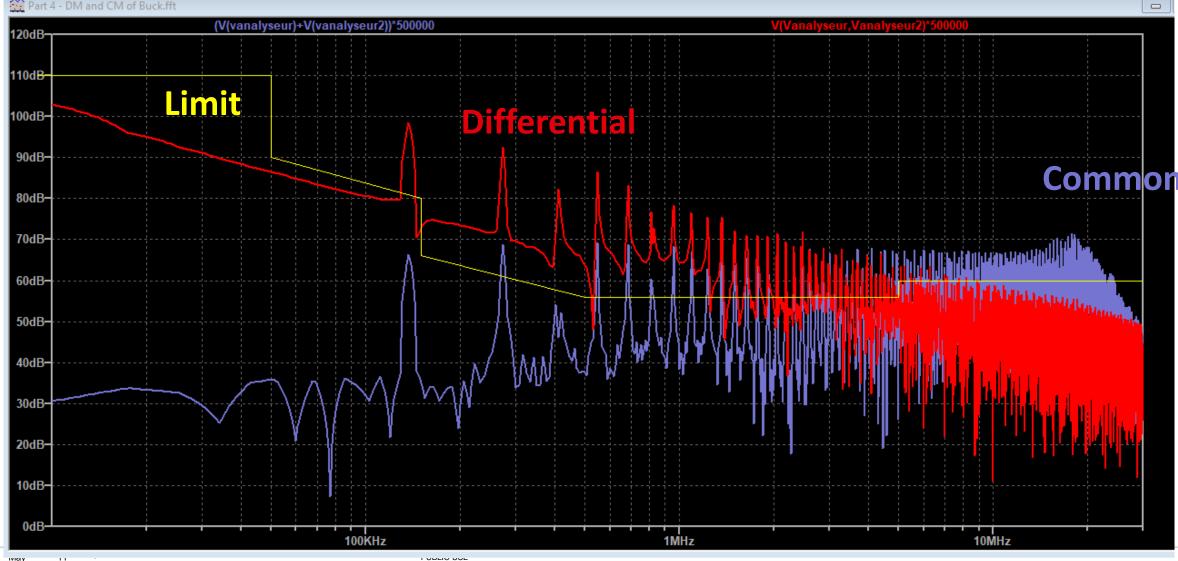

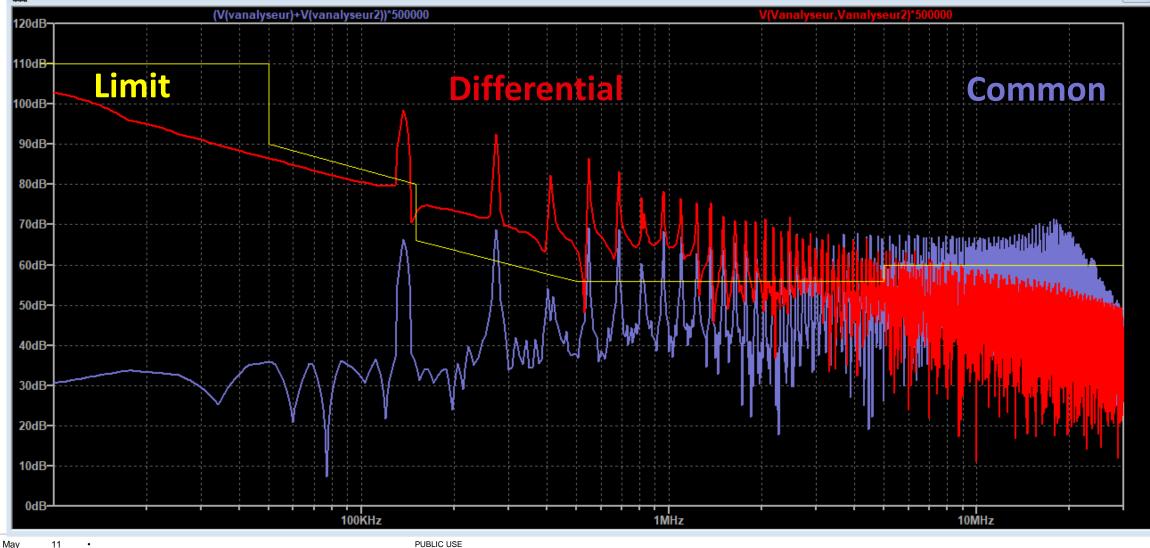

# **Going further with simulation** Making simulation look real – Result ©

Part 4 - DM and CM of Buck.fft

2020

© All rights reserved by Wurth Electronics. ights. All rights of disposal such as copying and redistribution rights with us.

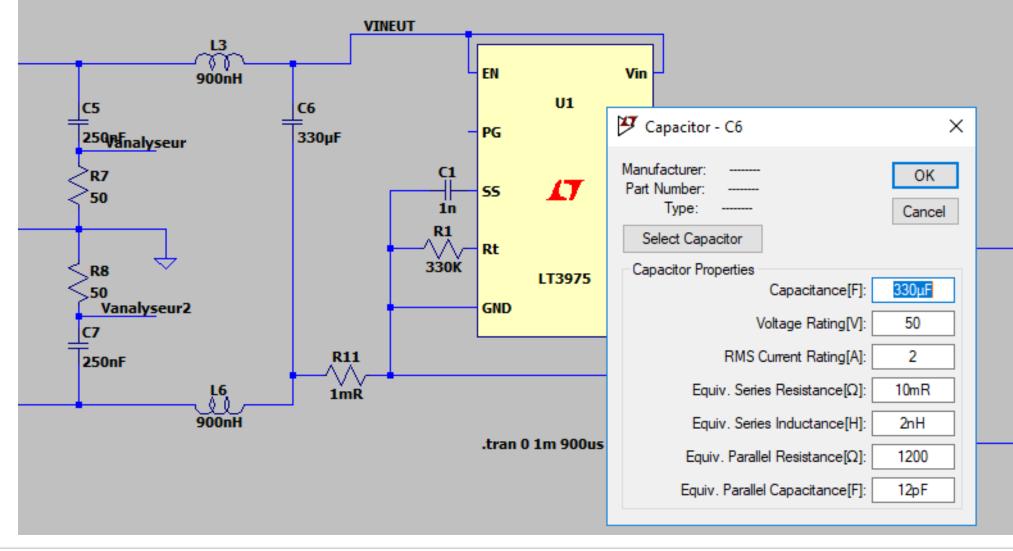

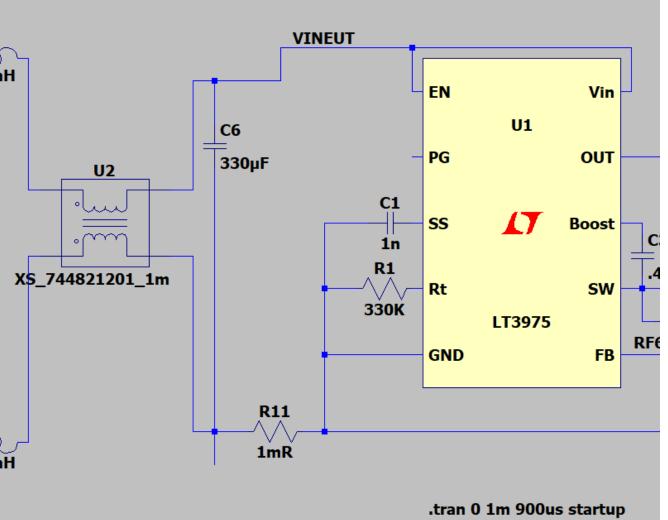

#### **Going further with simulation** Fixing that buck in the simulation – Polymer input cap

# Reality VS Simulation ESR / ESL / CAP breakdown in frequency

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

#### **Going further with simulation** Fixing that buck in the simulation – <u>Before</u> Polymer Cap

#### 🔐 Part 4 - DM and CM of Buck.fft

2020

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.co

#### **Going further with simulation** Fixing that buck in the simulation – <u>After</u> Polymer Cap

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

WÜRTH FIF

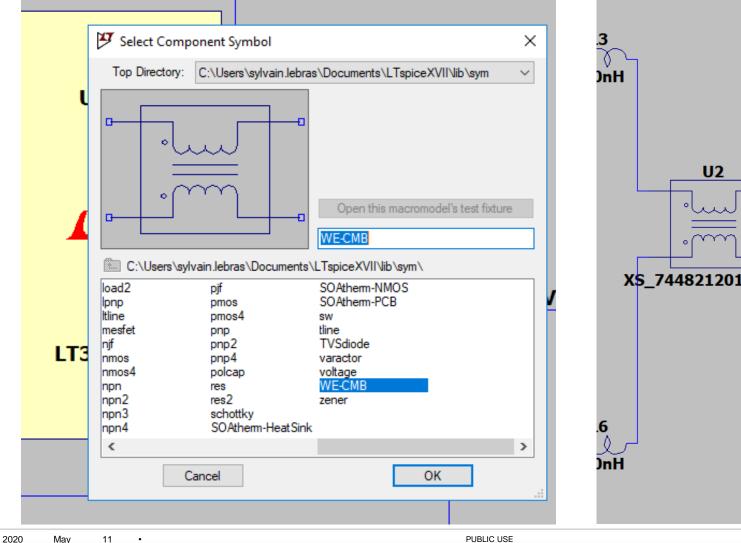

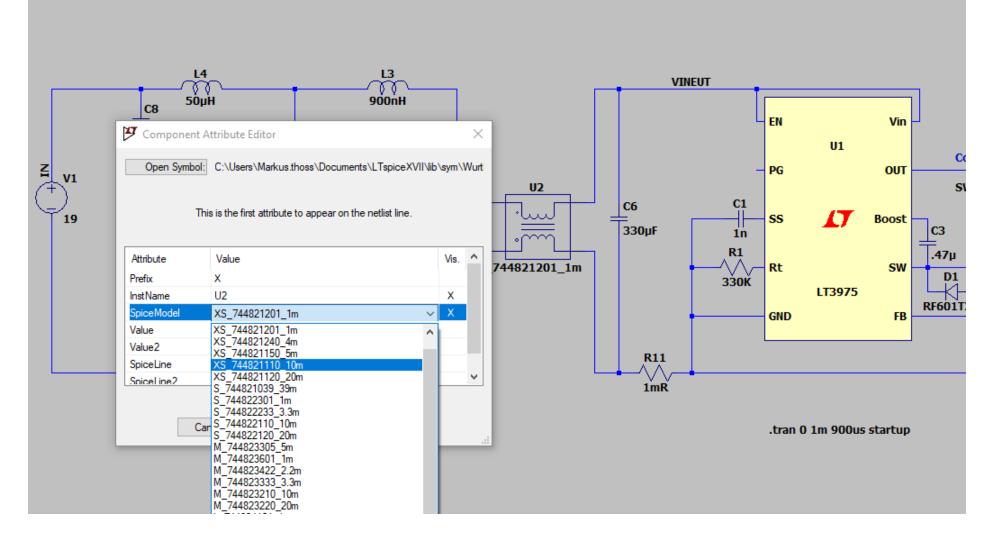

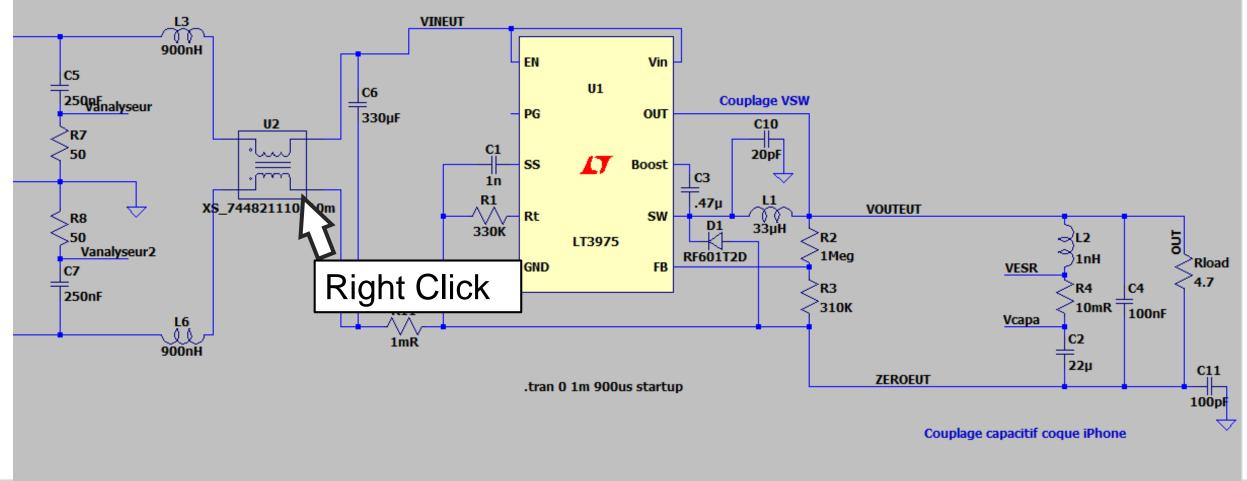

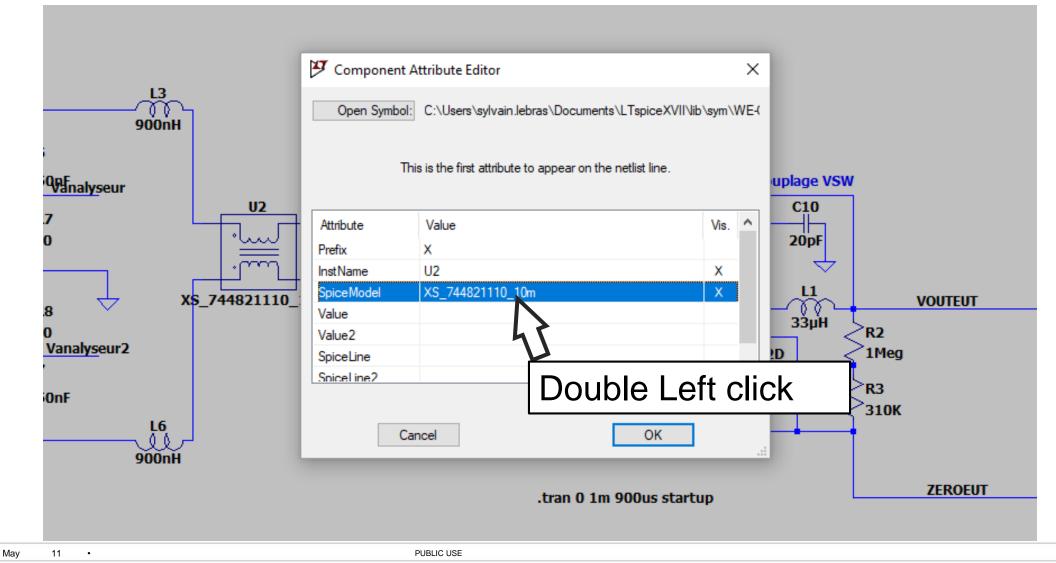

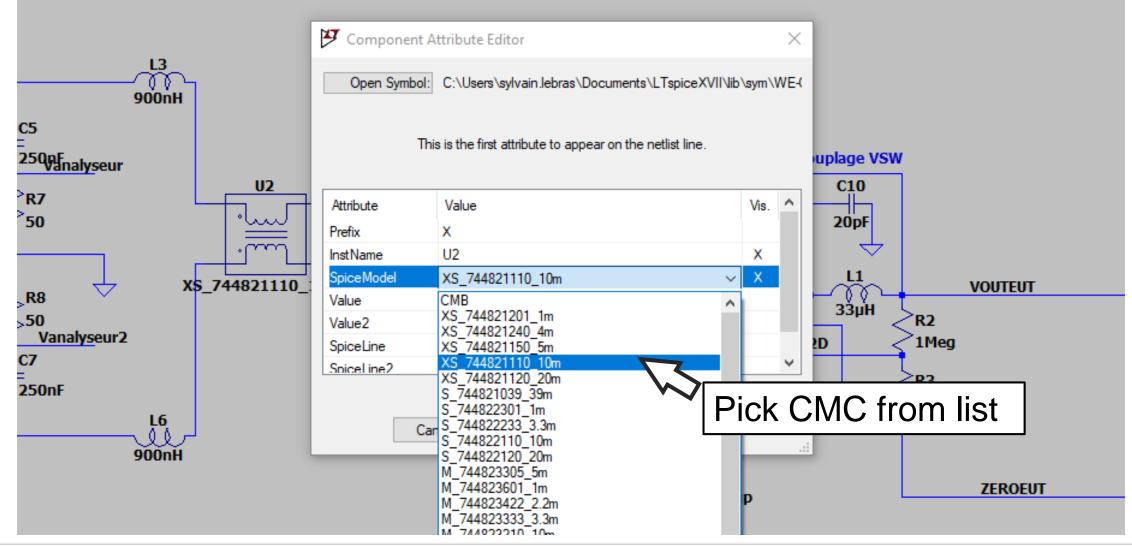

#### Going further with simulation Fixing that buck in the simulation – Common mode choke

Fixing that buck in the simulation – Input Common mode choke

•

Fixing that buck in the simulation – Input Common mode choke

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

PUBLIC USE

2020

11

٠

May

Fixing that buck in the simulation – Input Common mode choke

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

Fixing that buck in the simulation – Input Common mode choke

2020 May 11

#### **Going further with simulation** Fixing that buck in the simulation – <u>Without</u> Common mode choke

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

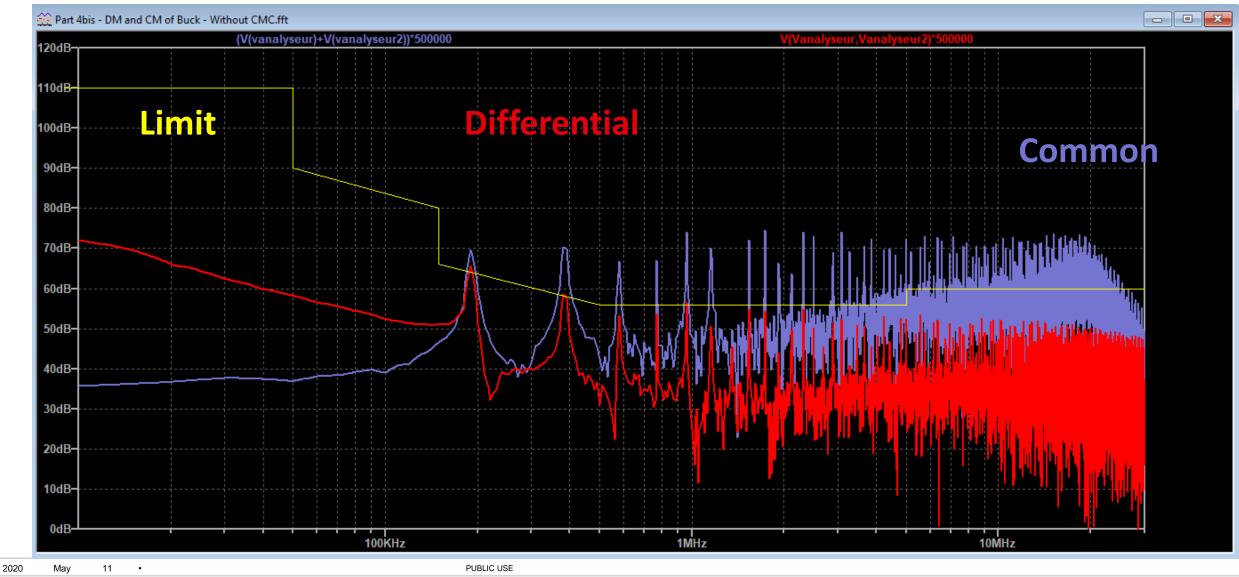

#### Fixing that buck in the simulation – With input Common mode choke

Part 4bis - DM and CM of Buck - Fixed.fft (V(vanalyseur)+V(vanalyseur2))\*500000 120dB 110d<del>B</del> Limit **Differential** 100dB Common 90dB 80dB 70dB 60dB 50dB 40dB 30dB 20dB 10dB 100KHz 1MHz 10MHz

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

PUBLIC USE

2020

May

11

#### **Going further with simulation** Fixing that buck in the simulation – <u>With</u> output CMC

2020 May 11

•

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

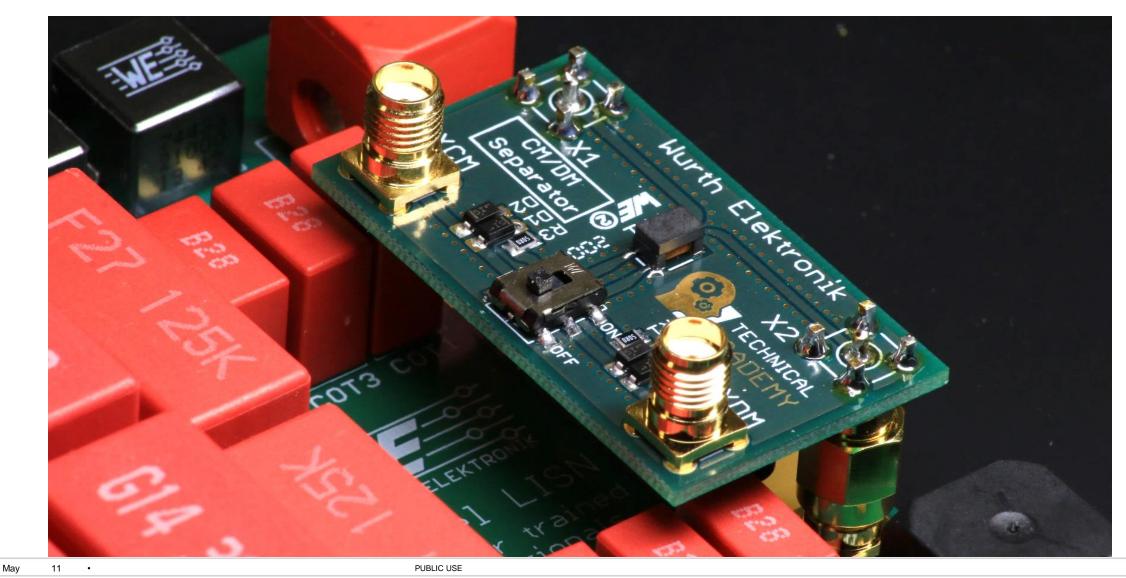

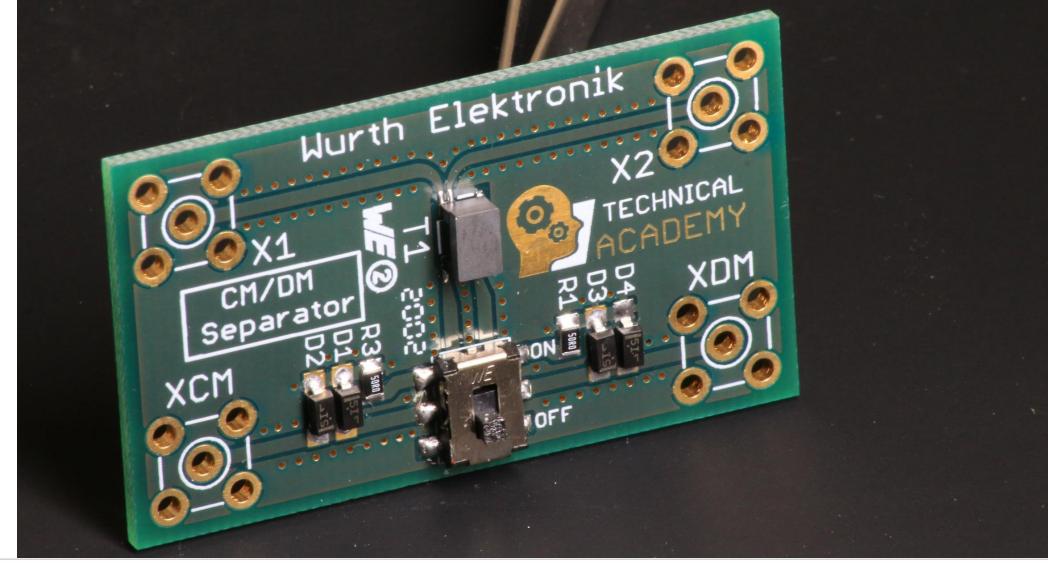

### **Going further ?** Common mode / Differential Mode separator in real life

2020

#### Going further ? Common mode / Differential Mode separator in real life

### **Going further ?** Common mode / Differential Mode separator in real life

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

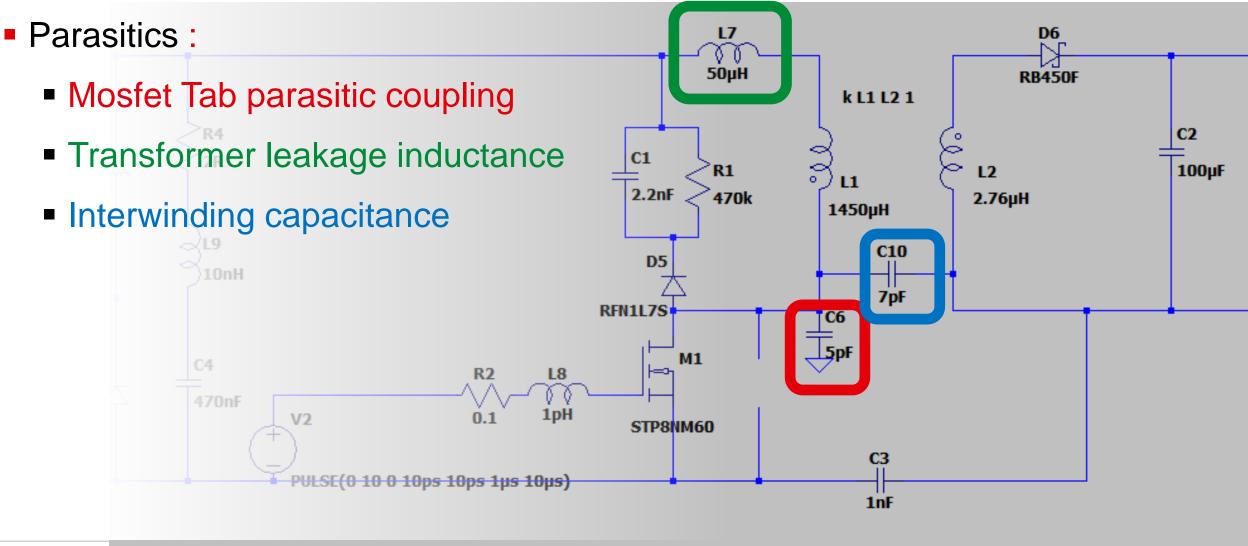

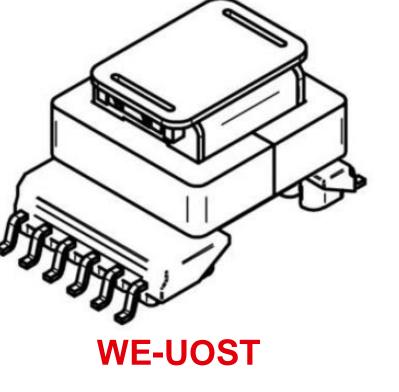

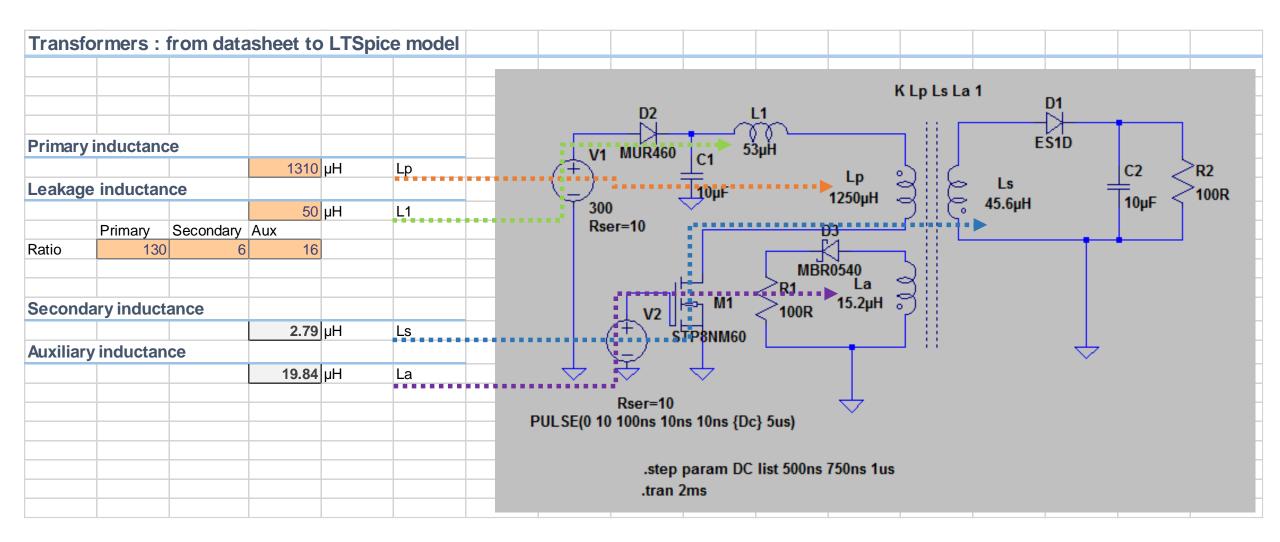

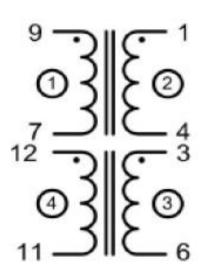

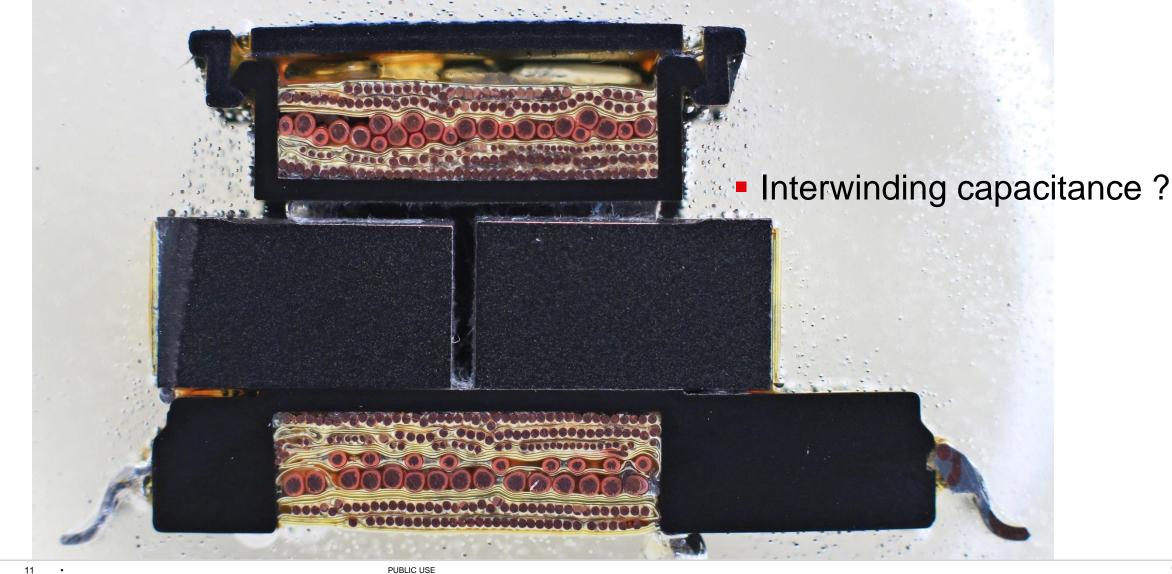

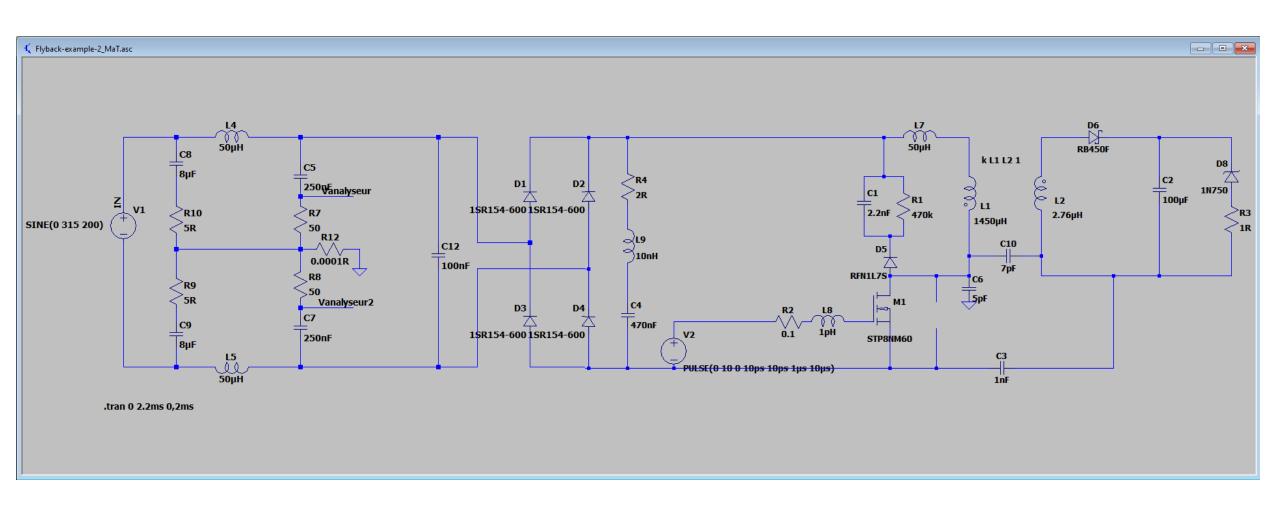

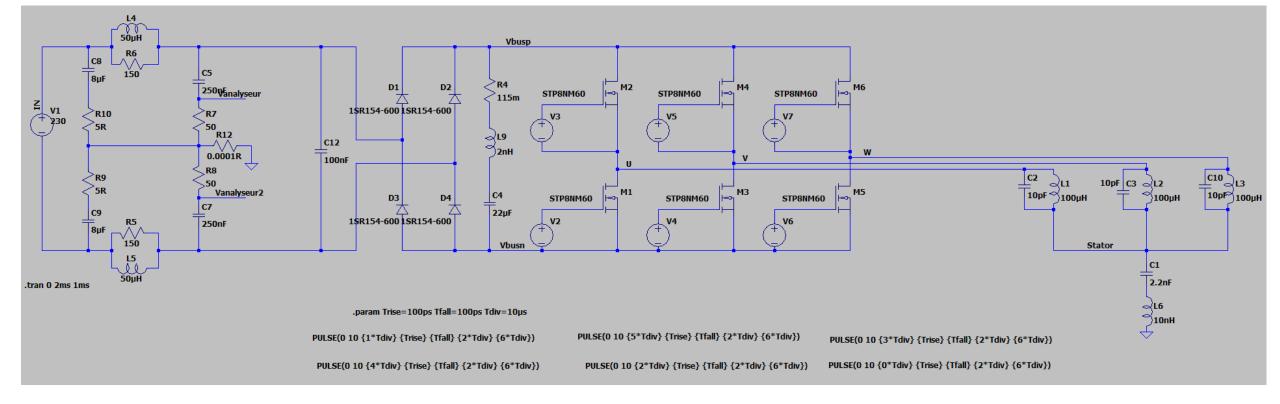

#### Modeling Real life examples Flyback converter for lighting applications

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

PUBLIC USE

2020

11

May

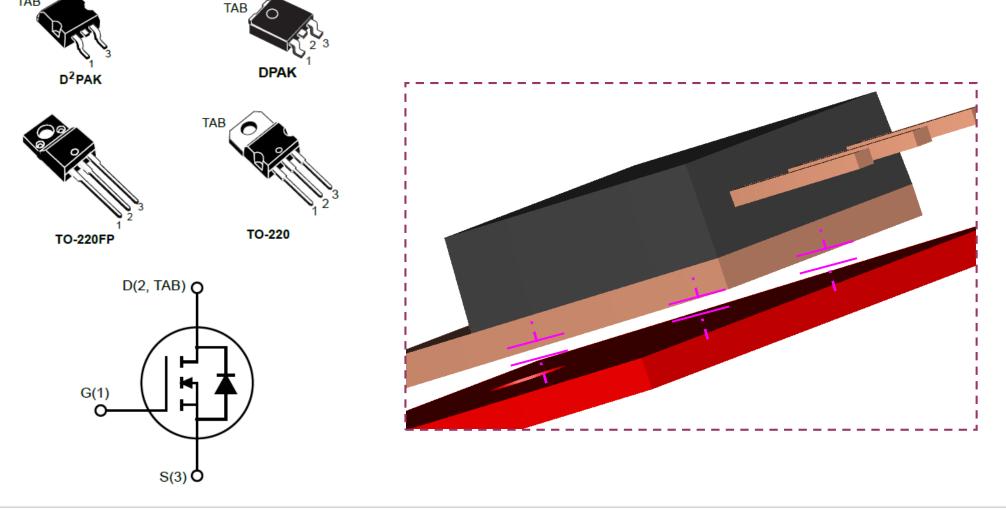

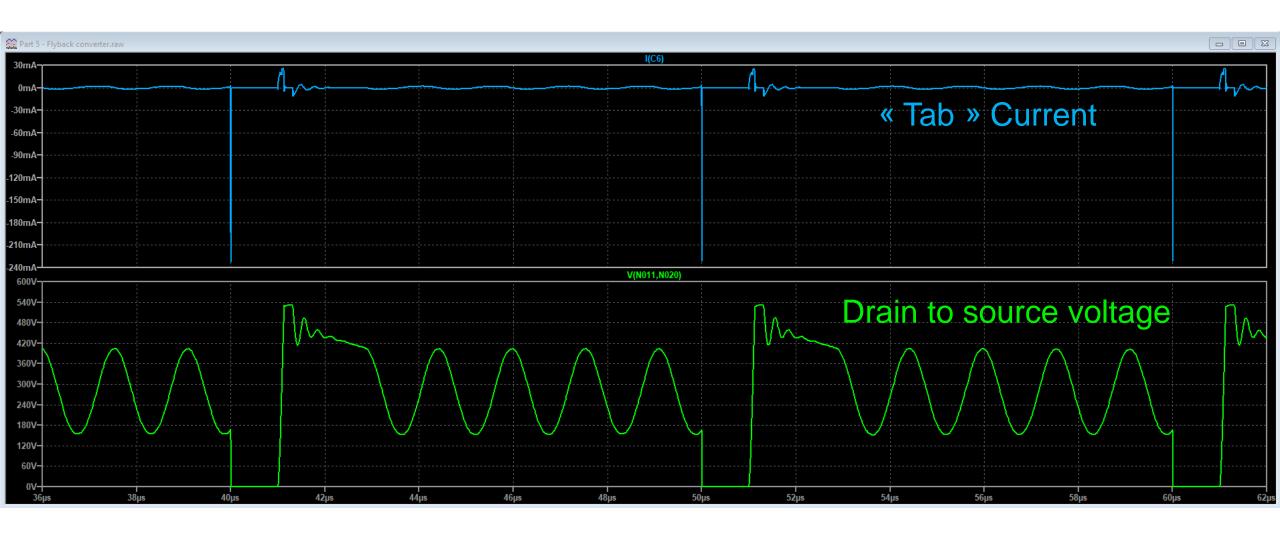

Mosfet Tab parasitic coupling

•

Mosfet Tab parasitic coupling

TAB

2020 May 11

Mosfet Tab parasitic coupling

2020 May 11

### Real life examples

Flyback converter for lighting applications

Primary leakage inductance

### **D Electrical Properties:**

| Properties              | Test conditions |                  | Value            | Unit   | Tol. |

|-------------------------|-----------------|------------------|------------------|--------|------|

| Inductance              | 100 kHz/ 100 mV | L                | 1310             | μH     | ±10% |

| Turns ratio             |                 | n                | 140 : 6 : 6 : 16 |        | ±3%  |

| Saturation current      | I∆L/LI < 20%    | I <sub>sat</sub> | 0.8              | А      | typ. |

| DC Resistance 1         | @ 20°C          | R <sub>DC1</sub> | 3000.0           | mΩ     | max. |

| DC Resistance 2         | @ 20°C          | R <sub>DC2</sub> | 25.0             | mΩ     | max. |

| DC Resistance 3         | @ 20°C          | R <sub>DC3</sub> | 25.0             | mΩ     | max. |

| DC Resistance 4         | @ 20°C          | R <sub>DC4</sub> | 450.0            | mΩ     | max. |

| Leakage inductance      | 100 kHz/ 100 mV | Ls               | 40.0             | μH     | max. |

| Insulation test voltage | W1,4 => W2,3    | ՍŢ               | 4000             | V (AC) |      |

2020 May 11

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

### Real life examples Turn ratio to inductance ?

Interwinding capacitance ?

|                                                                                             | 2 Ts tape |

|---------------------------------------------------------------------------------------------|-----------|

| N1 (8-7): Enameled copper wire<br>2 Layers with layer insulation                            | 3 Ts tape |

| N2 (1-4): Triple insulated wire<br>N3 (3-6): Triple insulated wire<br>Bifilar into 3 layers | 3 Ts tape |

| N4 (12-11): Enameled copper wire<br>Spread over 1 full Layer                                | 1 Ts tape |

| N1 (9-8): Enameleld copper wire<br>2 Layers with layer insulation                           |           |

2020 May 11

٠

2020

May

•

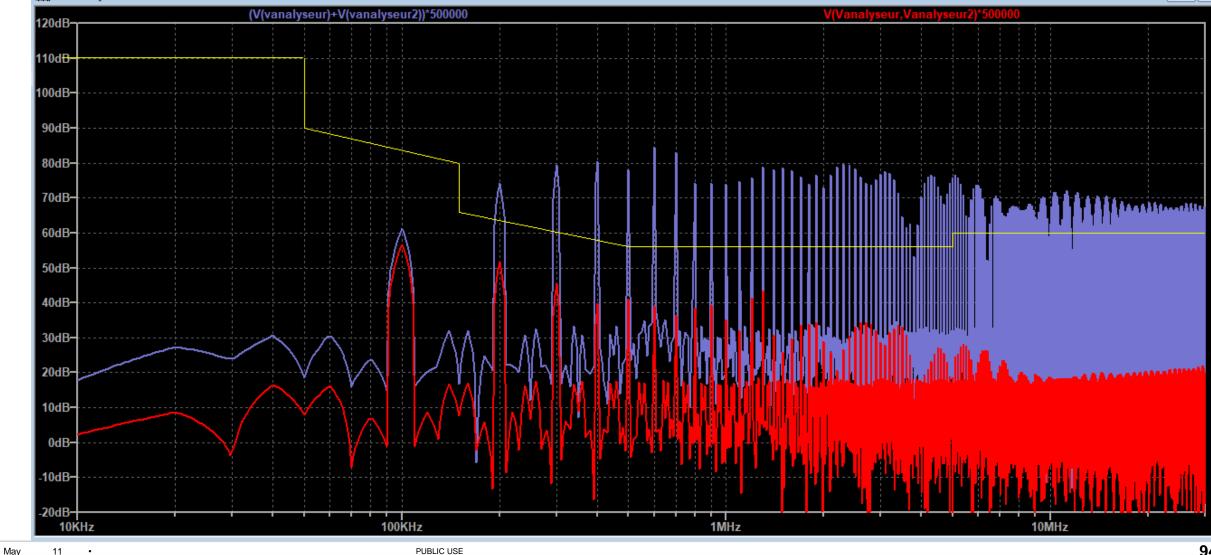

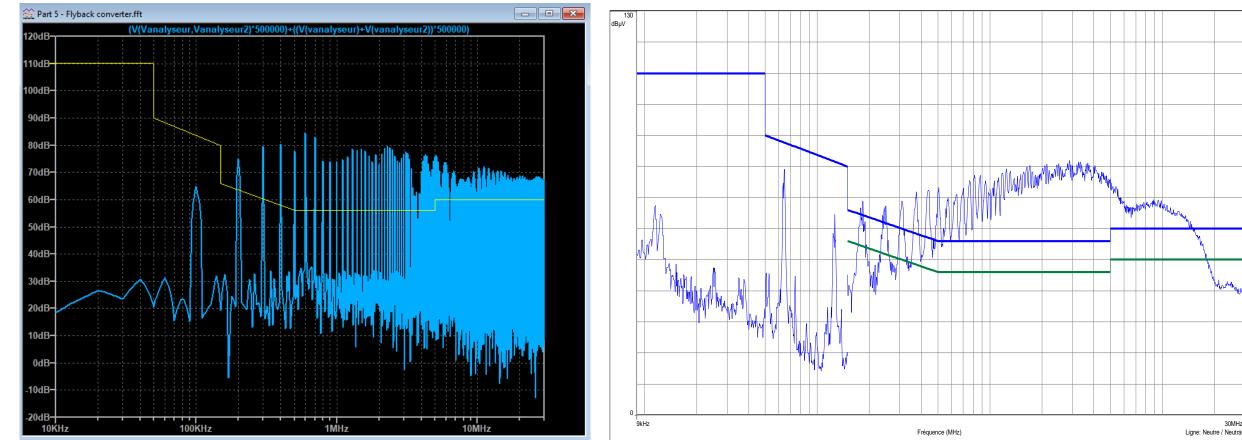

🚉 Part 5 - Flyback converter.fft

2020

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

### Simulation

### Example of actual measurement

2020 May 11

PUBLIC USE

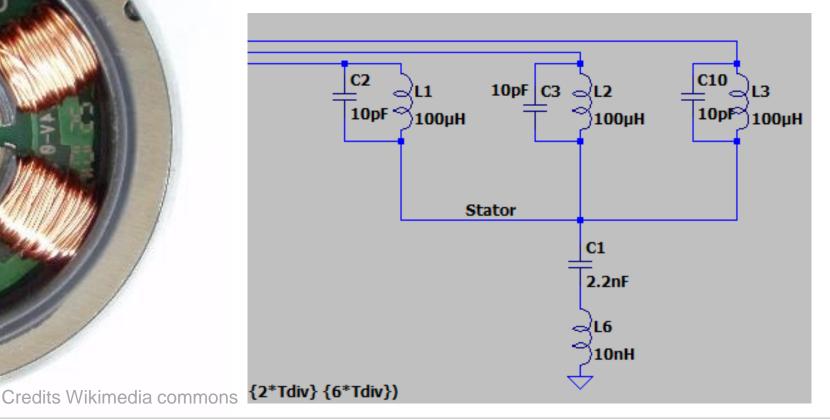

- Parasitic coupling to and through stator

- Influence of grounding

- Slew rate of driver

- Dead time impact

- Parasitic coupling to and through stator

- Influence of grounding (of stator)

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

2020

May

11

PUBLIC USE

17

C

PUBLIC USE

- Parametric simulation .param Trise=100ps Tfall=100ps Tdiv=10µs

- STEP is possible to see impact of slew rate and dead time on EMC signature

| Independent Voltage So                                                                                               | urce - V3                                                                                             |                                                                   |     | ×                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| ) (none)<br>) PULSE(V1 V2 Tdelay Tris                                                                                |                                                                                                       |                                                                   |     | DC Value:                                                                                                                               |

| ) SINE(Voffset Vamp Freq<br>) EXP(V1 V2 Td1 Tau1 Td<br>) SFFM(Voff Vamp Fcar MI<br>) PWL(t1 v1 t2 v2)<br>) PWL FILE: | 2 Tau2)                                                                                               | Brov                                                              | VSE | Small signal AC analysis(.AC)<br>AC Amplitude:<br>AC Phase:<br>Make this information visible on schematic: 🗹                            |

|                                                                                                                      | Vinitial[V]:<br>Von[V]:<br>Tdelay[s]:<br>Trise[s]:<br>Tfall[s]:<br>Ton[s]:<br>Tperiod[s]:<br>Ncycles: | 0<br>10<br>{1*Tdiv}<br>{Trise}<br>{Tfall}<br>{2*Tdiv}<br>{6*Tdiv} |     | Parasitic Properties         Series Resistance[Ω]:         Parallel Capacitance[F]:         Make this information visible on schematic: |

2020 May 11

Art 6 - BLDC and Inverter.fft

2020

May

© All rights reserved by Wurth Electronics, also in the of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

### Evaluation of Filter Insertion losses Design your EMC filter in LTspice

2020 May 11

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

### Evaluation of Filter Insertion losses Design your EMC filter in LTspice

#### V(VDMIL,VDMIH)@1/V(VDML,VDMH)@1

Filter 1 - DYEMC-Combined-CM-DM-CLC.asc

Place your filter Here Vgen v1 c2 v c3 c3 c3 c4 c3 c5 cM4 c50 c5 cm4 c5

•

### V(VDMIL,VDMIH)@2/V(vcm)@2

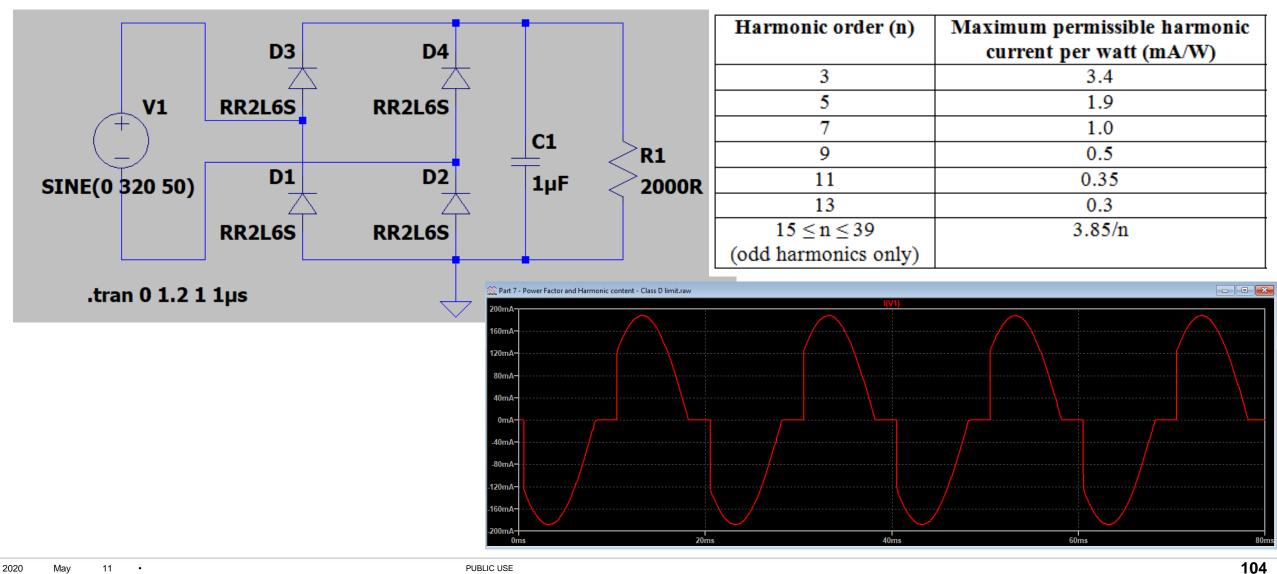

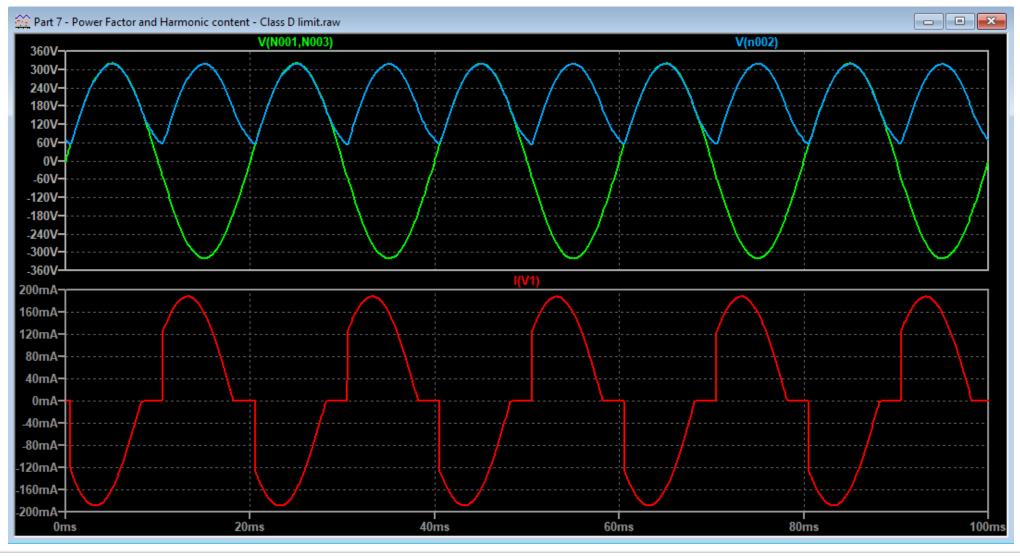

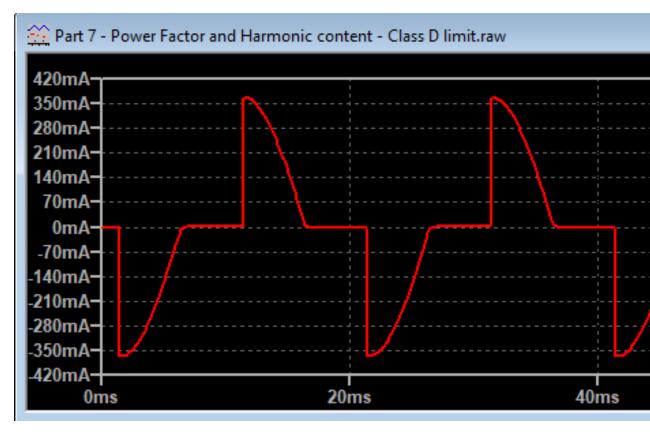

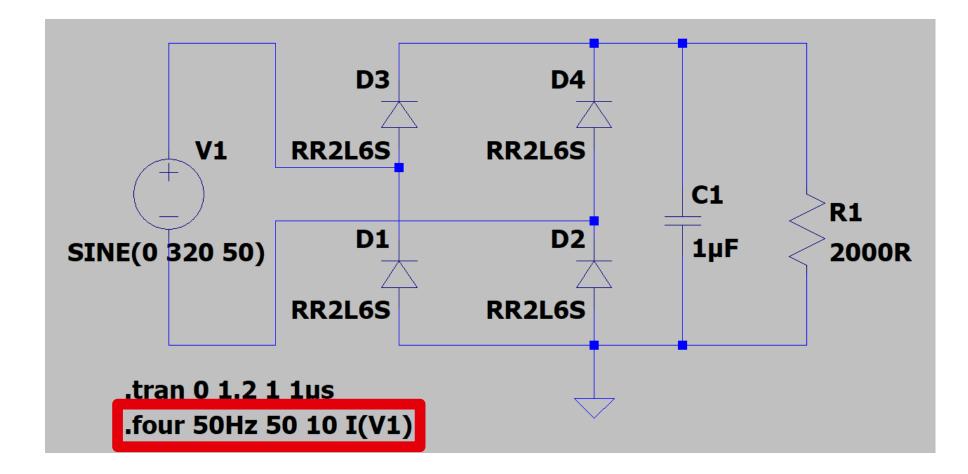

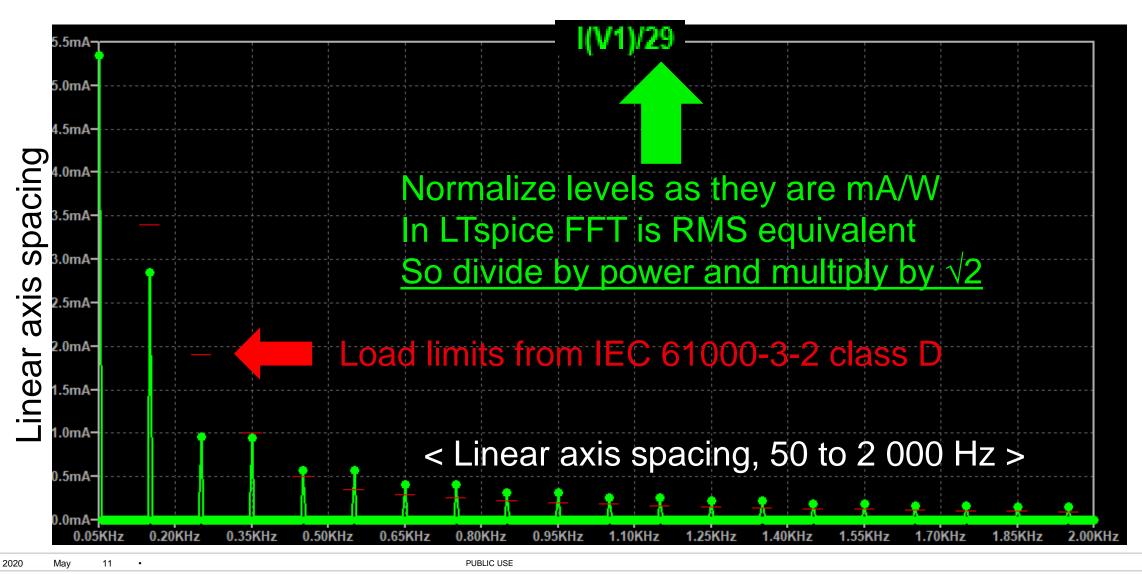

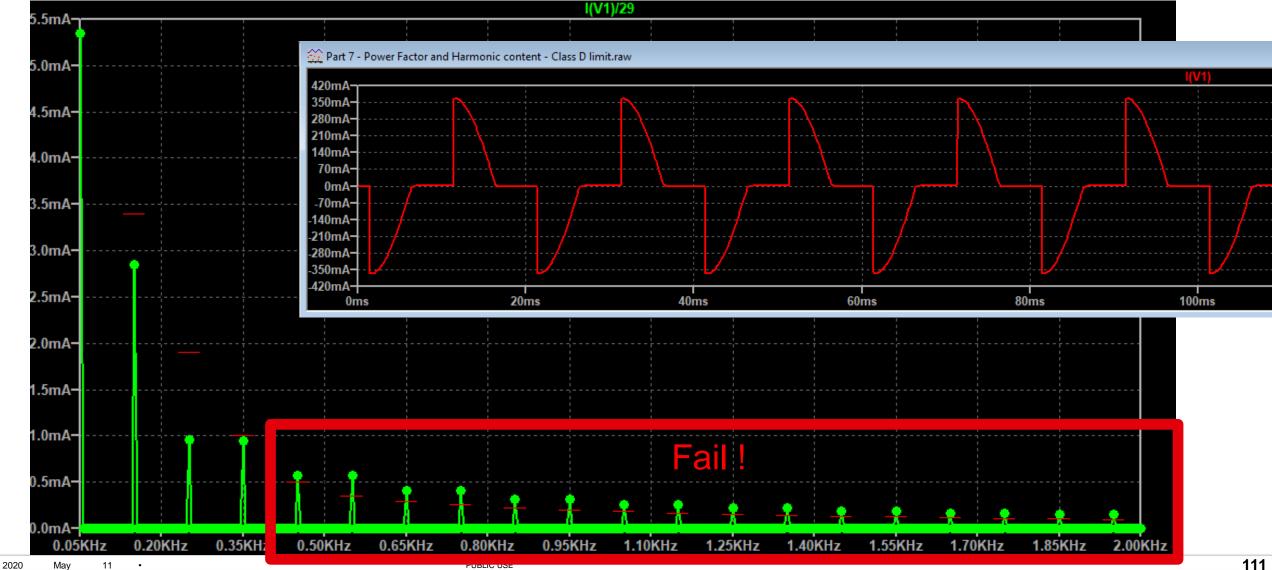

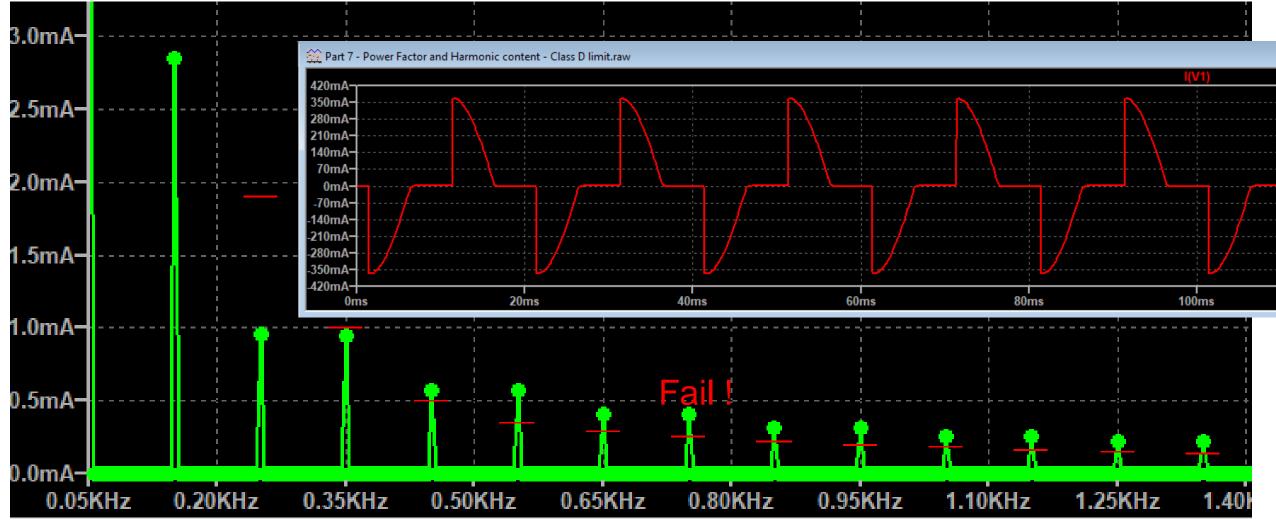

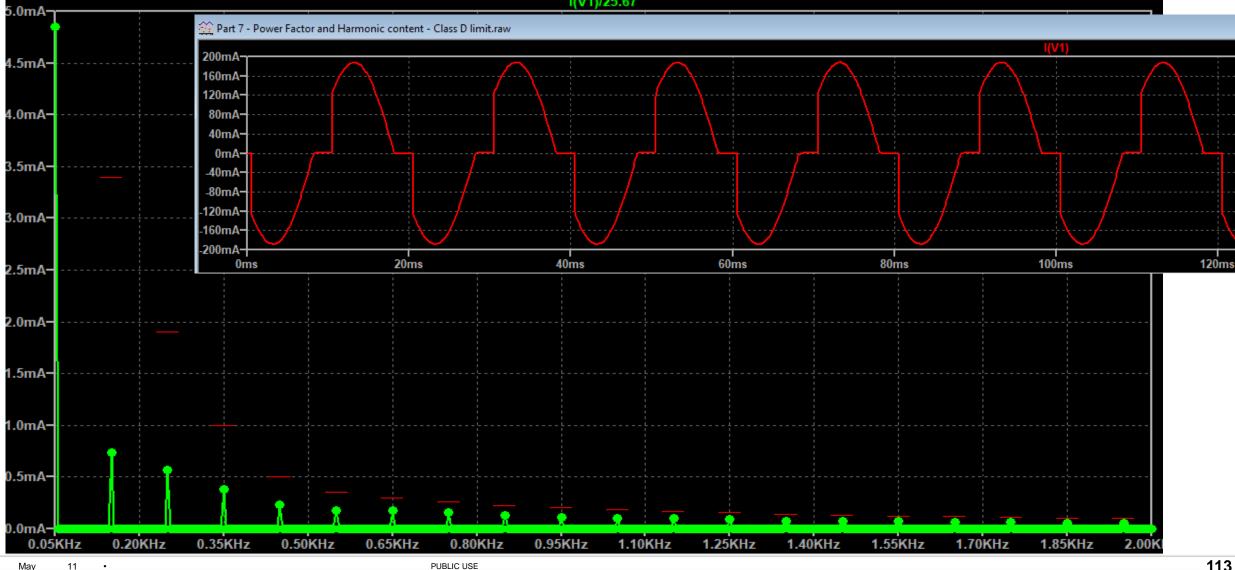

### **Power Factor and Harmonic current** Anticipate IEC 61000-3-2

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

### Power Factor and Harmonic current Anticipate IEC 61000-3-2

2020 May 11

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

### **Power Factor and Harmonic current** Anticipate IEC 61000-3-2

| Harmonic order (n)   | Maximum permissible harmonic<br>current per watt (mA/W) |

|----------------------|---------------------------------------------------------|

| 3                    | 3.4                                                     |

| 5                    | 1.9                                                     |

| 7                    | 1.0                                                     |

| 9                    | 0.5                                                     |

| 11                   | 0.35                                                    |

| 13                   | 0.3                                                     |

| $15 \le n \le 39$    | 3.85/n                                                  |

| (odd harmonics only) |                                                         |

2020 May 11

•

### **Power Factor and Harmonic current**

•

### **Power Factor and Harmonic current** .FOUR directive to Anticipate IEC 61000-3-2

$\times$

LTspice XVII - Part 7 - Power Factor and Harmonic cont Edit Hierarchy View Simulate Tools Windo File C 🕀 Zoom Area ┢╸ <u>کم</u> Ctrl+Z Zoom <u>B</u>ack Ctrl+B Fart 7 - Power Factor X Zoom to Fit 🕻 Part 7 - Power Fact 🏒 Pan Show Grid Ctrl+G Mark Unconn. Pins 'U' Mark Anchors 'A' Bill of Materials Efficiency Report SPICE Netlist SPICE Error Log S Xisible Traces Autorange <u>Y</u>-axis Marching Waves Set Probe Reference

| Fourier components of I(v1)<br>DC component:5.23172e-007 |           | Ampera    | fundame           | ntal     |            |

|----------------------------------------------------------|-----------|-----------|-------------------|----------|------------|

| Harmonic                                                 | Frequency | Fourier   | Normalized        | Phase    | Normalized |

| Number                                                   | [Hz]      | Component | Component         | [degree] | Phase [deg |

| 1                                                        | 5.000e+01 | 1.760e-01 | 1.000e+00         | -156.56° | 0.00°      |

| 2                                                        | 1.000e+02 | 3.265e-07 | 1.855e-06         | 57.75°   | 214.31°    |

| 3                                                        | 1.500e+02 | 2.687e-02 | 1.526e-01         | 102.46°  | 259.01°    |

| 4                                                        | 2.000e+02 | 1.123e-06 | 6.379e-06         | 2.94°    | 159.50°    |

| 5                                                        | 2.500e+02 | 2.074e-02 | 1.178e-01         | 108.42°  | 264.98°    |

| 6                                                        | 3.000e+02 | 2.040e-07 | 1.159e-06         | -164.89° | -8.33°     |

| 7                                                        | 3.500e+02 | 1.391e-02 | 7.904e-02         | 108.04°  | 264.59°    |

| 8                                                        | 4.000e+02 | 9.960e-07 | 5.658e-06         | -63.52°  | 93.04°     |

| 9                                                        | 4.500e+02 | 8.532e-03 | 4.847e-02         | 93.80°   | 250.36°    |

| 10                                                       | 5.000e+02 | 9.480e-07 | 5.386e-06         | 125.74°  | 282.30°    |

| 11                                                       | 5.500e+02 | 6.452e-03 | 3.665e-02         | 64.05°   | 220.61°    |

| 12                                                       | 6.000e+02 | 7.110e-07 | 4.039e-06         | -101.44° | 55.12°     |

| 13                                                       | 6.500e+02 | 6.362e-03 | 3.614e-02         | 41.96°   | 198.52°    |

| 14                                                       | 7.000e+02 | 1.526e-06 | 8.671e-06         | 51.93°   | 208.48°    |

| 15                                                       | 7.500e+02 | 5.865e-03 | 3.332e-02         | 29.38°   | 185.94°    |

| 16                                                       | 8.000e+02 | 4.225e-07 | 2.401e-06         | -89.14°  | 67.42°     |

| 17                                                       | 8.500e+02 | 4.761e-03 | 2.705e-02         | 14.64°   | 171.20°    |

| 18                                                       | 9.000e+02 | 1.168e-06 | 6.634e-06         | -50.15°  | 106.41°    |

| 19                                                       | 9.500e+02 | 3.923e-03 | 2.229e-02         | -8.40°   | 148.16°    |

| 20                                                       | 1.000e+03 | 8.830e-07 | 5.016e-06         | -105.51° | 51.05°     |

| 21                                                       | 1.050e+03 | 3.752e-03 | 2.131e-02         | -31.96°  | 124.60°    |

|                                                          |           | • • • • • | 0.005 05          | *** ***  | 05 000     |

| 45                                                       | 2.250e+03 | 1.732e-03 | 9.838e-03         | 98.91°   | 255.46°    |

| 46                                                       | 2.300e+03 | 7.944e-07 | 4.513e-06         | -44.86°  | 111.70°    |

| 47                                                       | 2.350e+03 | 1.685e-03 | 9.573e-03         | 77.95°   | 234.51°    |

| 48                                                       | 2.400e+03 | 1.657e-07 | 9.416e-07         | -81.86°  | 74.69°     |

| 10                                                       | 2 450e+03 | 1 6570-03 | 9 <b>/12</b> e=03 | 59.24°   | 215.79°    |

2020 May 11

### **Power Factor and Harmonic current**

Graphical method to anticipate IEC 61000-3-2

| EC 61000-3-2 Class D - LTSpice limit line calculator |    |            |          | e limit line calc |               |                                                              |

|------------------------------------------------------|----|------------|----------|-------------------|---------------|--------------------------------------------------------------|

|                                                      |    |            |          |                   |               |                                                              |

| in 50Hz ba                                           | se | Start Freq | End Freq | mA/W start        |               | Line def for LTSPICE plot settings file                      |

| Line                                                 | 3  | 130        | 170      | 3.4               | Line: "A" 40  | (130,0.0034) (170,0.0034)                                    |

| Line                                                 | 5  | 230        | 270      | 1.9               | Line: "A" 40  | (230,0.0019) (270,0.0019)                                    |

| Line                                                 | 7  | 330        | 370      | 1                 | Line: "A" 40  | (330,0.001) (370,0.001)                                      |

| Line                                                 | 9  | 430        | 470      | 0.5               | Line: "A" 40  | (430,0.0005) (470,0.0005)                                    |

| Line                                                 | 11 | 530        | 570      | 0.35              | Line: "A" 40  | (530,0.00035) (570,0.00035)                                  |

| Line                                                 | 13 | 630        | 670      | 0.296153846       | Line: "A" 4 0 | (630,0.000296153846153846) (670,0.000296153846153846)        |

| Line                                                 | 15 | 730        | 770      | 0.256666667       | Line: "A" 40  | (730,0.00025666666666666666666666666666666666                |

| Line                                                 | 17 | 830        | 870      | 0.226470588       | Line: "A" 4 0 | (830,0.000226470588235294) (870,0.000226470588235294)        |

| Line                                                 | 19 | 930        | 970      | 0.202631579       | Line: "A" 4 0 | (930,0.000202631578947368) (970,0.000202631578947368)        |

| Line                                                 | 21 | 1030       | 1070     | 0.183333333       | Line: "A" 4 0 | (1030,0.00018333333333333) (1070,0.000183333333333333)       |

| Line                                                 | 23 | 1130       | 1170     | 0.167391304       | Line: "A" 40  | (1130,0.000167391304347826) (1170,0.000167391304347826)      |

| Line                                                 | 25 | 1230       | 1270     | 0.154             | Line: "A" 40  | (1230,0.000154) (1270,0.000154)                              |

| Line                                                 | 27 | 1330       | 1370     | 0.142592593       | Line: "A" 4 0 | (1330,0.000142592592592593) (1370,0.000142592592592593)      |

| Line                                                 | 29 | 1430       | 1470     | 0.132758621       | Line: "A" 40  | (1430,0.000132758620689655) (1470,0.000132758620689655)      |

| Line                                                 | 31 | 1530       | 1570     | 0.124193548       | Line: "A" 40  | (1530,0.000124193548387097) (1570,0.000124193548387097)      |

| Line                                                 | 33 | 1630       | 1670     | 0.116666667       | Line: "A" 40  | (1630,0.000116666666666666666) (1670,0.00011666666666666666) |

| Line                                                 | 35 | 1730       | 1770     | 0.11              | Line: "A" 40  | (1730,0.00011) (1770,0.00011)                                |

| Line                                                 | 37 | 1830       | 1870     | 0.104054054       | Line: "A" 40  | (1830,0.000104054054054054) (1870,0.000104054054054054)      |

| Line                                                 | 39 | 1930       | 1970     | 0.098717949       | Line: "A" 4 0 | (1930,9.87179487179487E-05) (1970,9.87179487179487E-05)      |

2020 May

11

all rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.cor

© All rights reserved by property rights. All rights of disposal such as copying and redistribution rights with us. www.we-online.com

2020 May 11

© All rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us. www,we-online.com

pperty rights. All rights of disposal such as copying and redistribution rights with us, www.we-online.com

2020

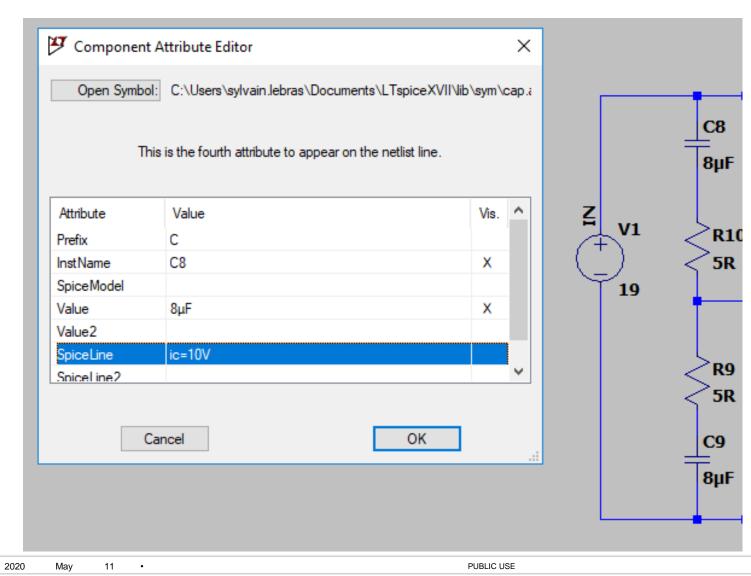

### Good to know Speed up simulations

### Setting initial condition

- Ctrl + Right Click

- SpiceLine

### **Questions**<sub>& Answers</sub>

#### Vous recevrez un lien avec les fichiers utilisés pendant cette présentation

Part 1 - Testfixture.asc Part 1 - Testfixture.plt Part 2 - Modified Testfixture - 1 output voltage.plt Part 2 - Modified Testfixture - 2 Breakdown.plt Part 2 - Modified Testfixture.asc Part 2 - Modified Testfixture.plt Part 3 - Ripple-Input-MD.asc Part 3 - Ripple-Input-MD-1 Time based display.plt Part 3 - Ripple-Input-MD-2 Frequency based display.plt Part 3 - Ripple-Input-MD-4 Frequency based display Breakdown.plt Part 4 - DM and CM of Buck - 1 FFT analysis.plt Part 4 - DM and CM of Buck - 2 Time based CMDM split.plt Part 4 - DM and CM of Buck - 3 FFT display of CMDM split.plt Part 4 - DM and CM of Buck.asc Part 4bis - DM and CM of Buck - Fixed.asc Part 5 - Flyback converter - 1 FFT split analysis.plt Part 5 - Flyback converter.asc Part 6 - BLDC and Inverter.asc Part 6 - BLDC and Inverter.log Part 6 - BLDC and Inverter.op.raw Part 7 - Power Factor and Harmonic content - Class D limit.asc Part 7 - Power Factor and Harmonic content - Class D limit.log Part 7 - Power factor and Harmonic content.plt Part 8 - DYEMC-Combined-CM-DM-CLC.asc Part 8 - DYEMC-Combined-CM-DM-CLC.plt

Slides and Simulation files are available here : https://github.com/sylvainlebras/anticipate-emc-with-Itspice

Schematic, Layouts, Bill of material, are released as open source : <u>https://github.com/sylvainlebras/EMC-Tools</u>

If you have questions:

Sylvain.LeBras@we-online.com