# **Starrflex in Verbindung mit USB3**

Würth Elektronik Circuit Board Technology

Webinar am 10.10.2017

**Referent: Andreas Schilpp**

# **Agenda**

Zusammenfassung, Q&A

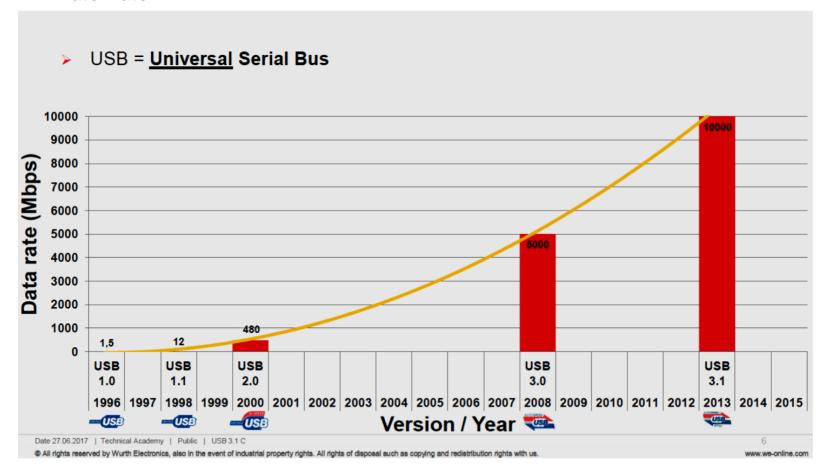

- Entwicklung USB = Universal Serial Bus

- Datenrate

source: WE USB3.X Kongress

- Entwicklung USB = Universal Serial Bus

- Benchmark

- Based on Microsoft tests: (showed at WinHEC 2008 on Nov 6)

Transfer of a 25GB Blu-ray movie:

USB 1.1: <u>9.3 hours</u> ← **× 40**

USB 2.0: 13.9 minutes

USB 3.0: <u>70 seconds</u>

| USB version | Data rate |  |

|-------------|-----------|--|

| USB 1.0     | 1,5 Mbps  |  |

| USB 1.1     | 12 Mbps   |  |

| USB 2.0     | 480 Mbps  |  |

| USB 3.0     | 5 Gbps    |  |

| USB3.1Gen.2 | 10 Gbps   |  |

Date 27.06.2017 | Technical Academy | Public | USB 3.1 C

all rights reserved by Wurth Electronics, also in the event of industrial property rights. All rights of disposal such as copying and redistribution rights with us.

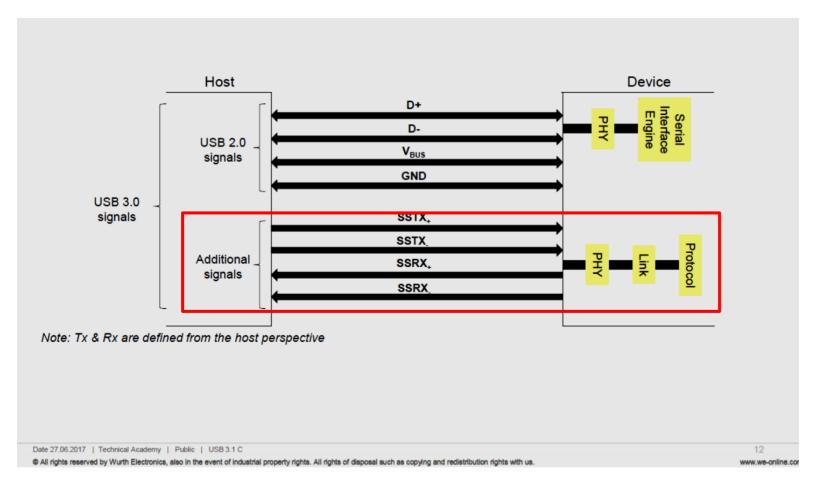

zusätzliche Leitungen: 2x diff. pairs

source: WE USB3.X Kongress

- USB (Universal Serial Bus)

Zdiff

90 ohms

- LVDS (Low-Voltage-Differential Signaling)

Zdiff

100 ohms

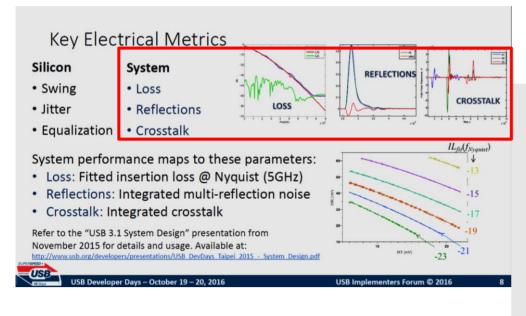

#### Herausforderung für die Leiterplatte:

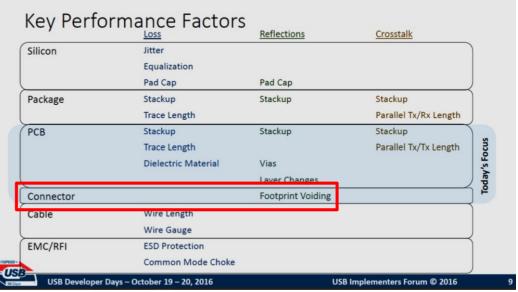

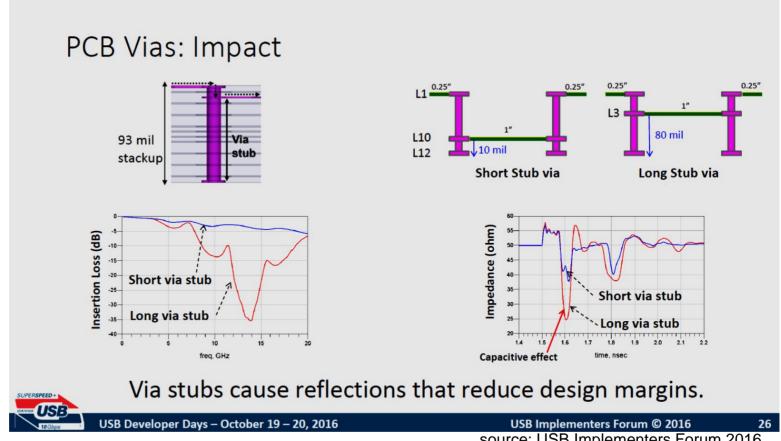

source: USB Implementers Forum 2016

#### Lösungsansatz: Microvias und Starrflex

Vermeidung von THV wo möglich

source: USB Implementers Forum 2016

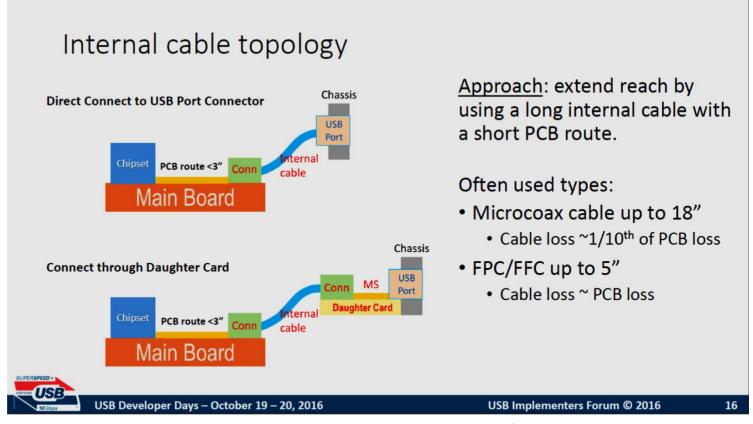

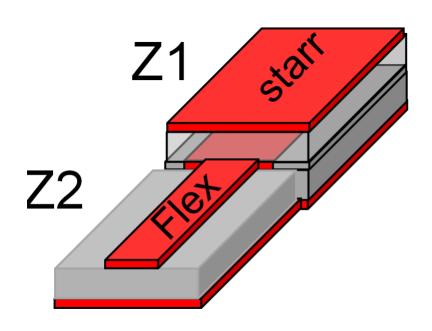

#### Lösungsansatz: Starrflex

- low-loss Material Polyimid

- Eliminierung der Schwachstelle Stecker

source: USB Implementers Forum 2016

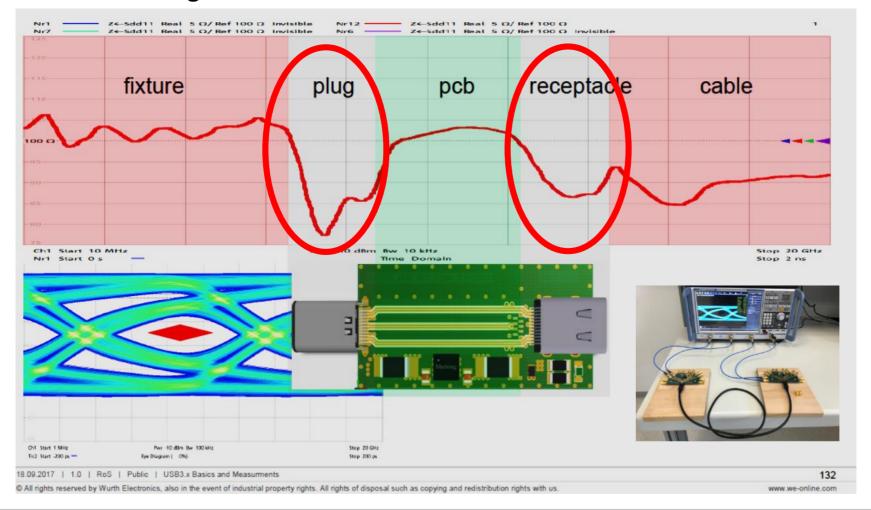

#### Schnittstellen Interfaces

#### Lösungsansatz: Starrflex

Eliminierung der Schwachstelle Stecker

source: WE USB3.X Kongress

# **Agenda**

#### Signalintegrität und Leiterplatte

#### Kernthemen:

- Impedanz Leistungsanpassung

- Laufzeit / Gruppenlaufzeit (Timing)

- Reflexionen

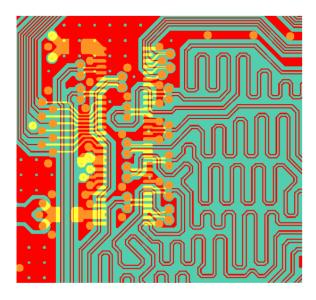

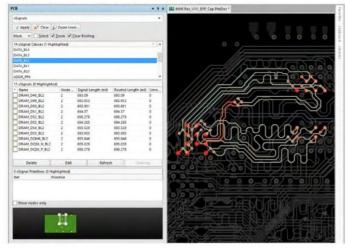

#### Beispiel aus USB3-Schaltung:

Figure 2: Automatically generated xSignal Class of all Byte Lane 2

specific Data xSignals

Source: Altium

#### **Hinweis:**

Mehr Informationen zu Signalintegrität bei Starrflex: Webinar Archiv

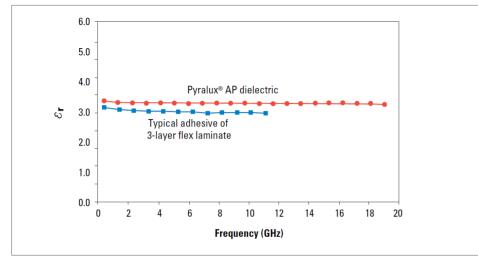

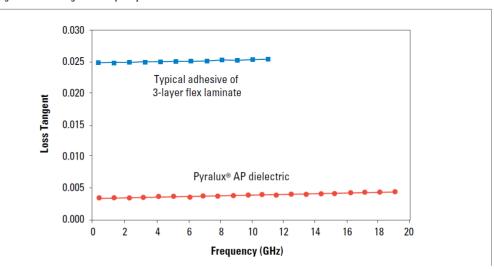

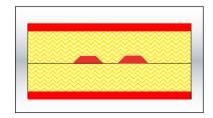

#### Besonderheiten bei Starrflex: Flexmaterial Polyimid

- grundsätzlich günstig für hohe Frequenzen durch

- geringe Verluste durch kleines tanδ

- geringe Verluste durch sehr flaches Treatment des Kupfers

- grundsätzlich "Handlungsbedarf" wegen

- kleiner Dielektrizitätskonstante

- geringe Dicken, typ. 50μm

Figure 7. Loss Tangent vs. Frequency

www.we-online.de

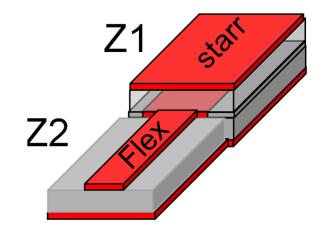

#### Besonderheiten bei Starrflex

$$Z_{\text{flex}} = Z_{\text{rigid}}$$

#### <u>Lösungsansatz:</u>

- Zielimpedanz festlegen

- Impedanzmodell auswählen

- H der Flexlage wählen (Dicke PI)

- (! 75µm / 100µm PI sind Preistreiber!)

- ? Gibt es mechanische Anforderungen (Biegeradien, dynamische Biegungen)?

- Simulation: Leiterbahnbreiten anpassen.

W<sub>min</sub> mit LP-Hersteller absprechen

- "Hatch" Option Referenzlage

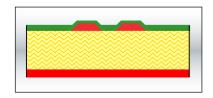

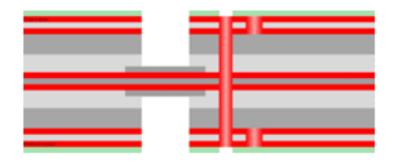

#### Lagen Konfiguration: 2-lagig im Flex- / Biegebereich

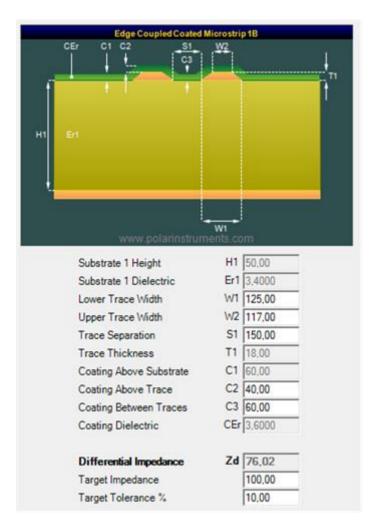

#### **Edge Coupled Coated Microstrip – mit 1 Referenzlage**

Starrflex xRi–2F–xRi

FR4 Semiflex 2Ri–xRi

#### **Lagen Konfiguration:** > 2-lagig im Flexbereich

#### Stripline – mit 2 Referenzlagen

Starrflex > xRi-2F-xRi, z.B. 1Ri-6F-1Ri

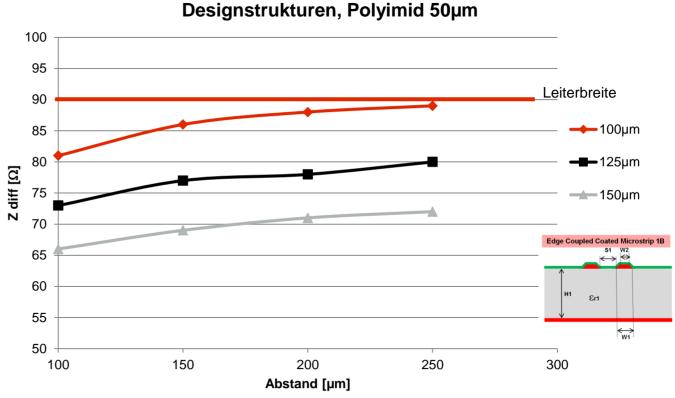

### **Auswirkung line / space Parameter**

# **Agenda**

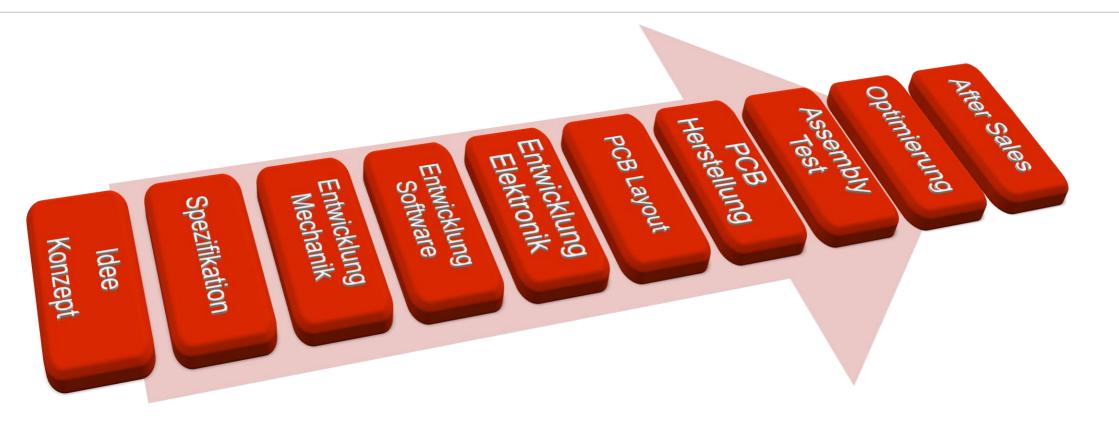

## Design Chain Elektronikentwicklung

Mehr zu diesem Thema finden Sie <u>hier</u>

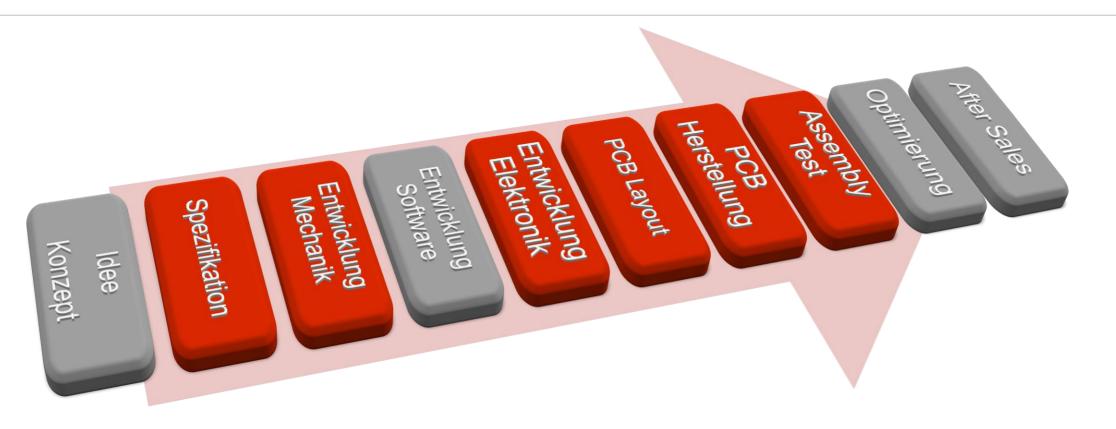

### Design Chain für Starrflex bei hohen Datenraten

relevante Punkte mit Input für folgenden Ablauf

## Ablauf "Starrflex mit Impedanz Spezifikationen"

#### Bauteile

- Stack-up (Standard)

- Via Technologie

#### Mechanik

- Check Platzbedarf (Anordnung, Testcoupon?)

- Kostenoptimierung

#### SI Spezi

- Anpassung Stack-up

- Impedanzrechnung, Dokumentation

- Angebot Starrflex Leiterplatte

#### Elektronik Design

- Bestellung mit Dokumentation, Herstellung Prototypen LP

- mit / ohne Testcoupon, mit / ohne Impedanzmessung (Serie?)

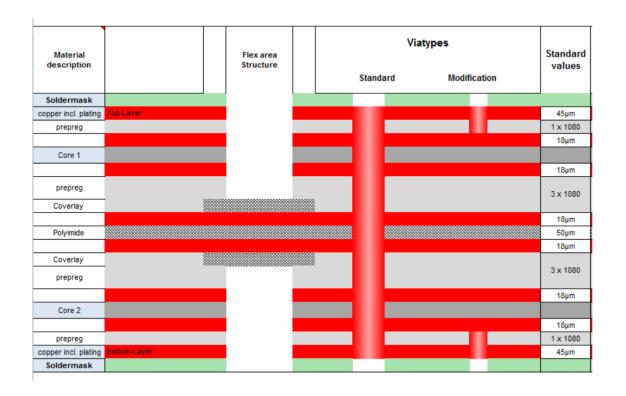

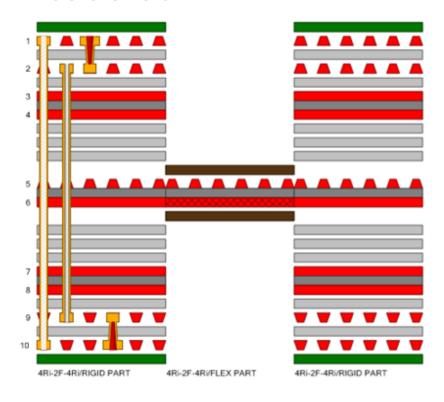

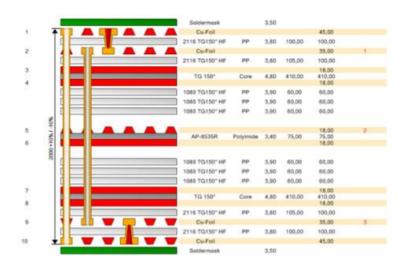

#### **Standard Lagenaufbauten Starrflex**

- Basismaterial Standard xRi-2F-xRi Aufbauten

- Starr: FR4 Tg ≥150°C, halogenarm, gefüllt

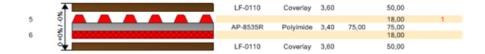

- Flex: Polyimid Tg > 200°C typisch 50µm dick

- Lötstopplack, Polyimid Deckfolien (Coverlay) partiell im Biegebereich

- Innenlagenkupfer 18µm

#### TIPP:

Anfragen gerne per email an die Teamadresse:

flex@we-online.de

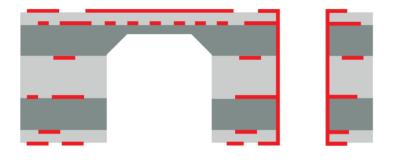

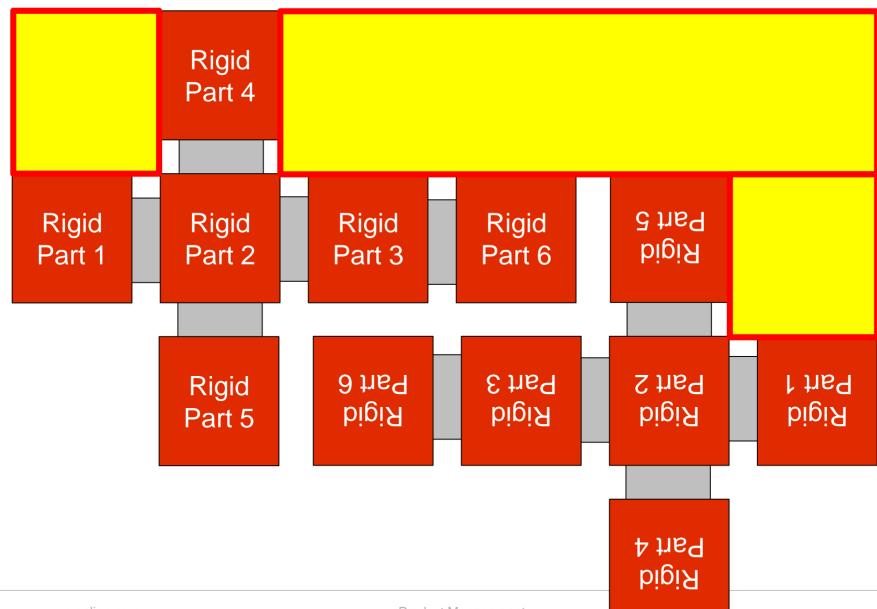

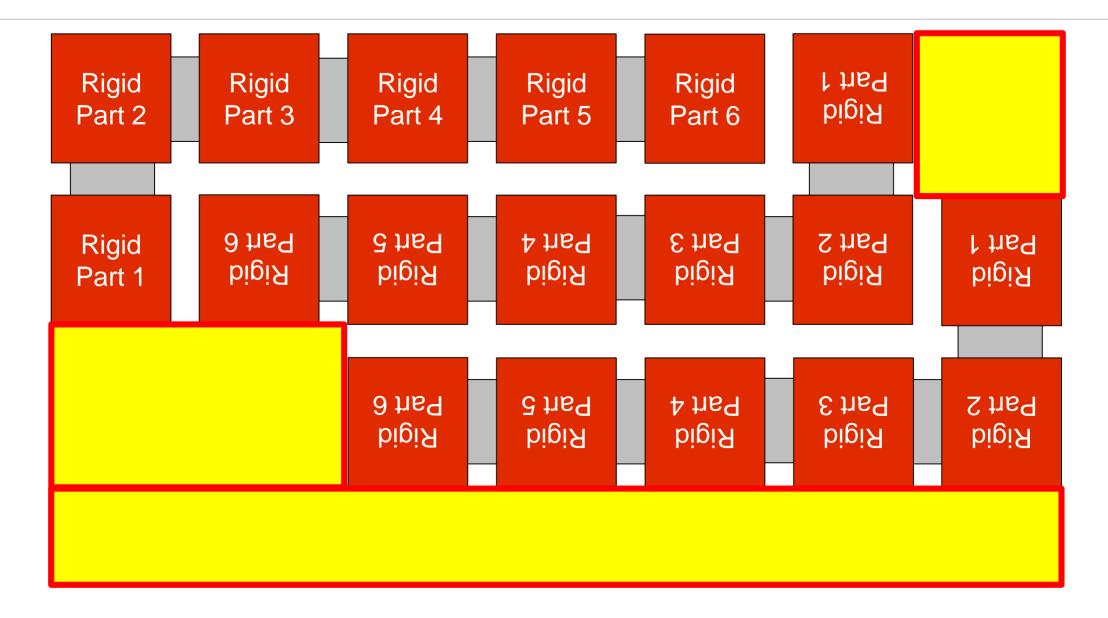

# Mechanik Konstruktion Platzbedarf verschiedener Anordnungen

Rigid Part 2

Rigid Part 3

Rigid Part 4

Rigid Part 5

Rigid Part 6

# Mechanik Konstruktion Platzbedarf "Kreuz"

# Mechanik Konstruktion Platzbedarf "L-Form"

# Mechanik Konstruktion Platzbedarf "Linie"

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

|--------|--------|--------|--------|--------|--------|

| Part 1 | Part 2 | Part 3 | Part 4 | Part 5 | Part 6 |

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

| Part 1 | Part 2 | Part 3 | Part 4 | Part 5 | Part 6 |

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

| Part 1 | Part 2 | Part 3 | Part 4 | Part 5 | Part 6 |

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

| Part 1 | Part 2 | Part 3 | Part 4 | Part 5 | Part 6 |

# Mechanik Konstruktion Platzbedarf "Matrix"

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

|--------|--------|--------|--------|--------|--------|

| Part 1 | Part 2 | Part 3 | Part 1 | Part 2 | Part 3 |

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

| Part 4 | Part 5 | Part 6 | Part 4 | Part 5 | Part 6 |

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

| Part 1 | Part 2 | Part 3 | Part 1 | Part 2 | Part 3 |

| Rigid  | Rigid  | Rigid  | Rigid  | Rigid  | Rigid  |

| Part 4 | Part 5 | Part 6 | Part 4 | Part 5 | Part 6 |

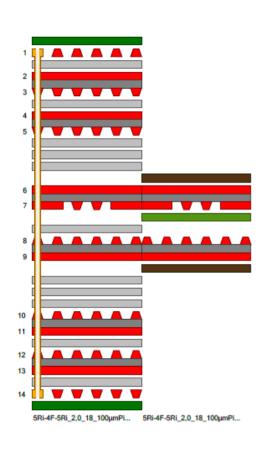

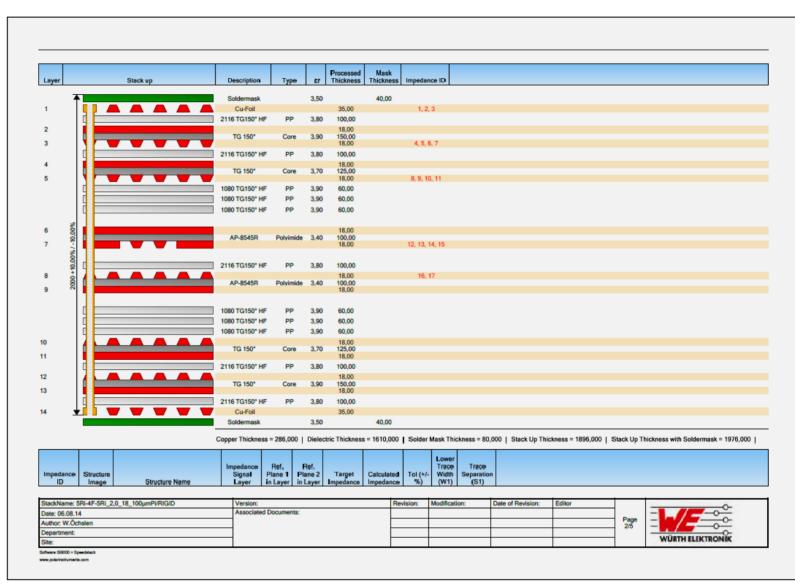

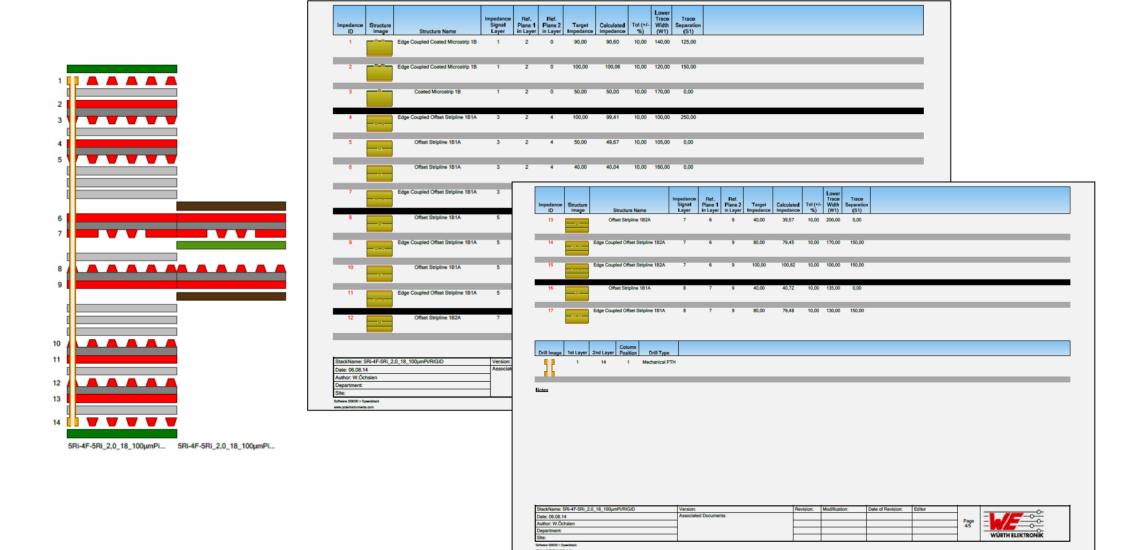

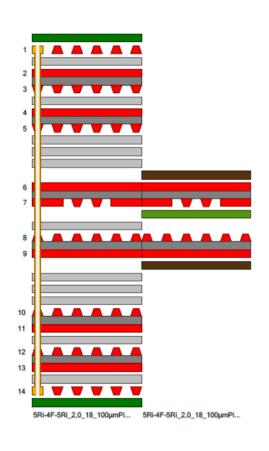

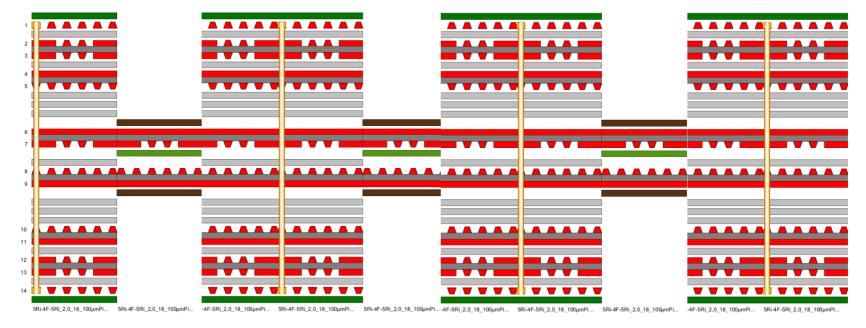

### **Anpassung Stack-up**

#### Masteransicht:

#### Betrachtung Starrbereich:

#### Betrachtung Flexbereich:

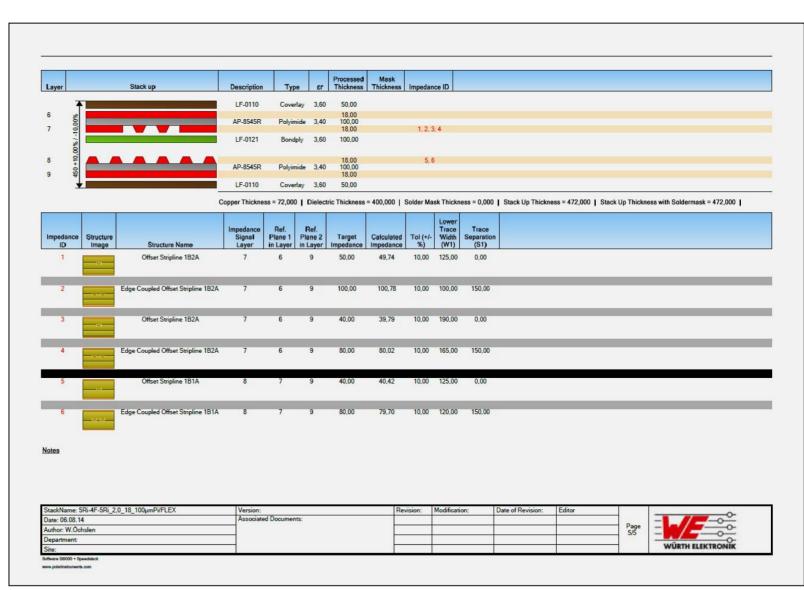

## **Berechnung und Dokumentation 5Ri-4F-5Ri**

## Berechnung und Dokumentation 5Ri-4F-5Ri

### **Berechnung und Dokumentation 5Ri-4F-5Ri**

# **Agenda**

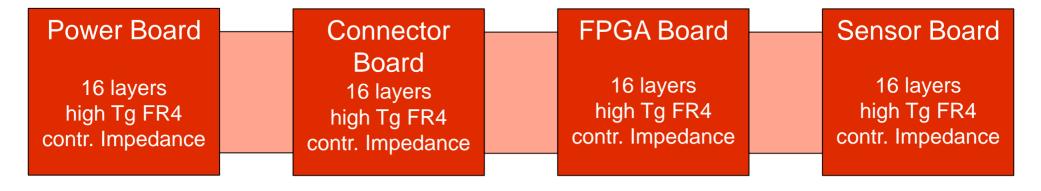

# **Anwendungsbeispiel Ausgangssituation**

**Power Board**

8 layers FR4 Connector

Board

10 layers

FR4

contr. Impedance

€

**FPGA Board**

16 layers high Tg FR4 contr. Impedance

**Sensor Board**

10 layers FR4 contr. Impedance

Abbildung beispielhaft

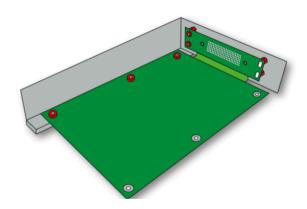

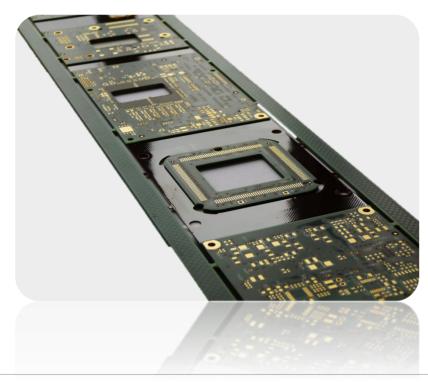

### Anwendungsbeispiel Lösungsansatz: Starrflex xRi-4F-xRi

# **Anwendungsbeispiel Ergebnis: Starrflex 4Ri-4F-4Ri**

**Power Board**

12 layers high Tg FR4 contr. Impedance Connector

Board

12 layers

high Tg FR4

contr. Impedance

**FPGA Board**

12 layers high Tg FR4 contr. Impedance **Sensor Board**

12 layers high Tg FR4 contr. Impedance

Miniaturisierung, Performance, Testbarkeit

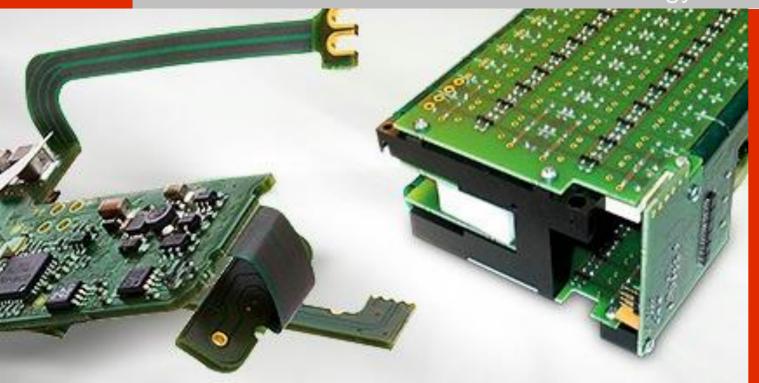

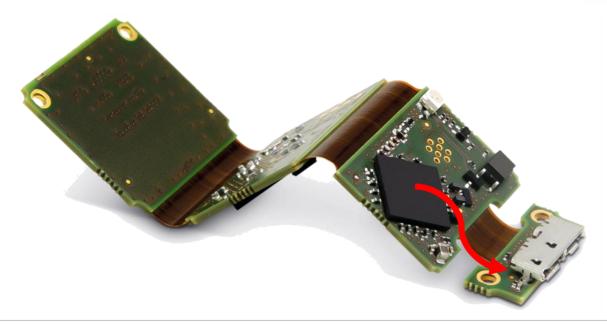

### **USB3 Kamera – Miniaturisierung par excellence!**

- USB Stecker auf extra Starrteil

- impedanzkontrollierte Verbindung über Flexbereich

- Vermeidung Stecker, Einsparung Footprints

- Verwendung von Microvias

- exzellente Performance

- gute Testbarkeit

- gute Robustheit

# **Agenda**

Schnittstellen Signalintegrität bei Starrflex Design Chain – Ablauf Entwurf Beispiele Zusammenfassung, Q&A

#### Zusammenfassung

#### Starrflex für hohe Datenraten, wie z.B. USB3

- hohe Datenraten verlangen nach verbesserten Leiterplattenlösungen

- Starrflex hat dafür klare systemische Vorteile

- die Komplexität der Elektronikgeräte Entwicklung verlangt eine mit dem Leiterplattenhersteller eng abgestimmte Vorgehensweise

- Würth Elektronik hat Erfahrung mit Impedanz gefertigten Starrflex Leiterplatten

- Für die Umsetzung von USB3.1 Gen.2 in miniaturisierten Systemen wird Starrflex notwendig sein

### Danke für Ihre Aufmerksamkeit!

## Die Kenntnis der Zusammenhänge ist ein Erfolgsgeheimnis!

## Vielen Dank für Ihre Aufmerksamkeit!

Andreas Schilpp WÜRTH ELEKTRONIK GmbH & Co. KG Senior Product Manager

Circuit Board Technology T.: +49 7940 946 330

E. andreas.schilpp@we-online.de W. www.we-online.de/flex