### Designing efficient EV charging systems with C2000<sup>™</sup> real-time MCUs

### Agenda

- EV chargers overview

- DC/DC : Dual active bridge

- C2000 PWM

- AC/DC: Vienna rectifier, ANPC PFC

- C2000 Overview

### **EV** charging

#### **DC** fast charger

#### 50-150kW+ charging station

- + Offers filling gas like experience for EVs

- Modular architecture made up of multiple racks of 25-50kW AC:DC & DC:DC power modules

- + Can support V2G

- Cost

- Needs infrastructure power line upgrade

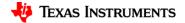

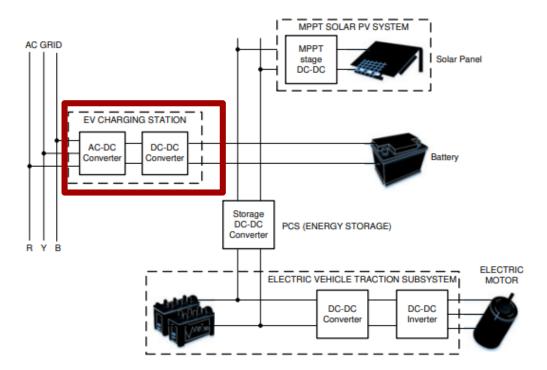

### V2G: Bidirectional power flow concept

### Agenda

- EV chargers overview

- DC/DC: Dual active bridge

- C2000 PWM

- AC/DC: Vienna rectifier, ANPC PFC

- C2000 overview

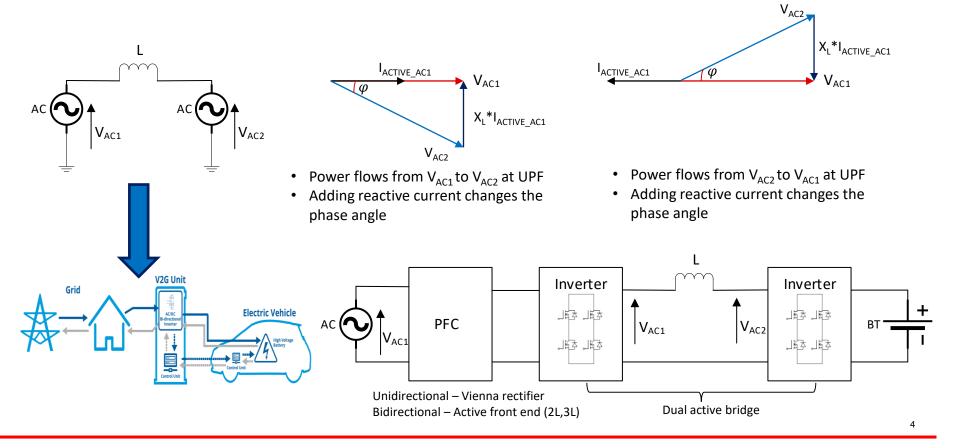

### Single phase shift - Dual active bridge (DAB)

$$\mathsf{P} = \frac{V_{GRID}V_{BATT}n\varphi(\pi - |\varphi|)}{2\pi^2 F_{SW}L}$$

n = transformer turns ratio $\varphi = phase shift between the bridges$  $\pi, \varphi$  are in radians

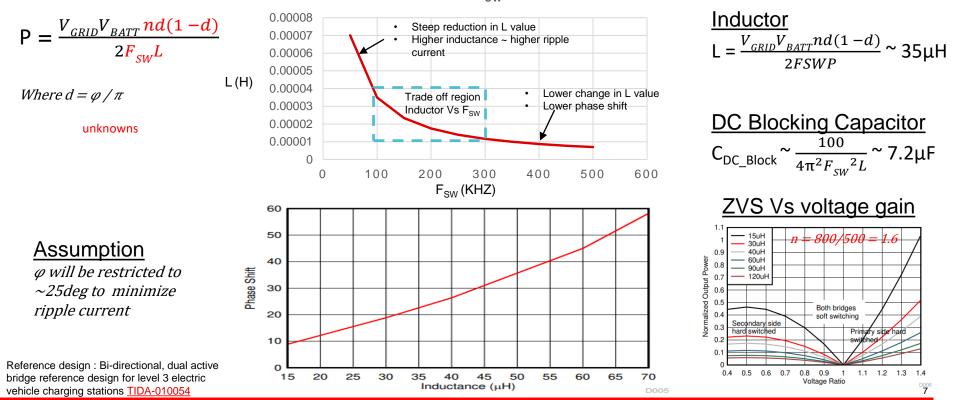

$$\mathsf{P} = \frac{V_{GRID}V_{BATT}nd(1-d)}{2FSWL}$$

Where  $d = \varphi / \pi$

### **DAB : Simplified design considerations**

L VS F<sub>SW</sub>

TEXAS INSTRUMENTS

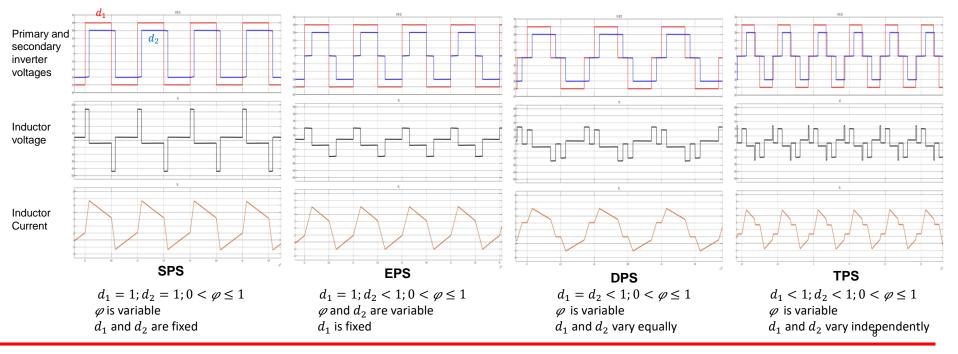

### Multi-phase shift DAB

- DAB when operated away from unity voltage ratio and rated power, the SPS control technique leads to low efficiency, high RMS and peak currents.

- Dual phase shift and triple phase shift controls make DAB more efficient

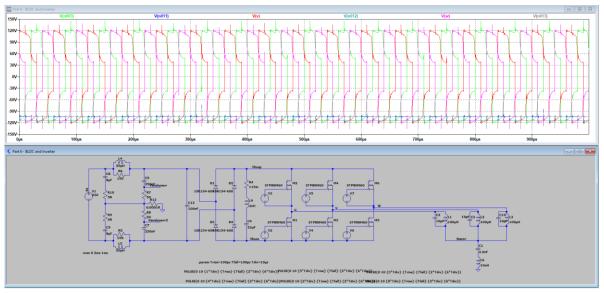

### **HR-phase shift and synchronization**

- *φ* -> 0 to ~25deg controlling 10KW Output power

- 0 to ~25deg at 100KHz corresponds to ~690nsec

- PWM module operating at 100MHz can have a resolution of 10ns

- *Minimum adjustable output power = 10KW \* 10/690 ~ 145W*

- Its not uncommon to have single DAB power module rated for 50KW

- C2000 real-time MCU

- With high resolution phase shift of 150ps enables finer control

- Up to 16 high resolution PWM channels

- Synchronization of multiple ePWM modules controlling intra and inter bridge phase shifts

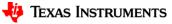

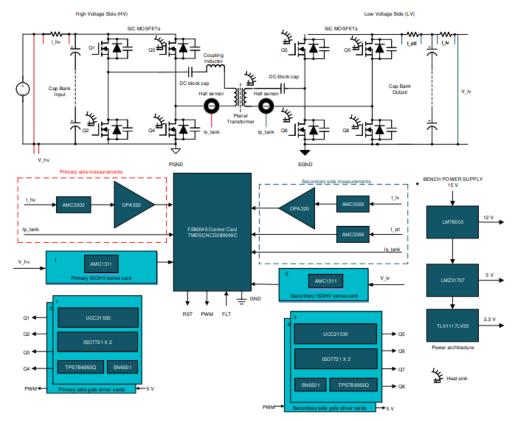

### **Controlling DAB with C2000**

PWM -

PWM -

- Built-in analog comparators against a 12bit DAC with 50ns pin-to-pin response time → enable real-time system protection against over-current & over-voltage events

- Trip any or all PWMs asynchronously to the system clock and independently from processing bandwidth

- Optimized C28x core, CLA and TMU enable fast execution of the control loop for advanced multiphase DAB

- FPU unit built in  $\rightarrow$  no more coding concern of scaling, overflow/underflow

- C2000 MCU with TMU can execute trigonometric & division operations, such as a "sine" instruction in 4 pipelined cycles. This compares with up to 41 cycles on an MCU without TMU → ~10x performance improvement

- PLLs or software algorithms that use transforms benefit greatly from the TMU

CLA – Control law accelerator TMU – Trigonometric math unit

savings

### Agenda

- EV chargers overview

- DC/DC: Dual active bridge

- C2000 PWM

- AC/DC: Vienna rectifier, ANPC PFC

- C2000 overview

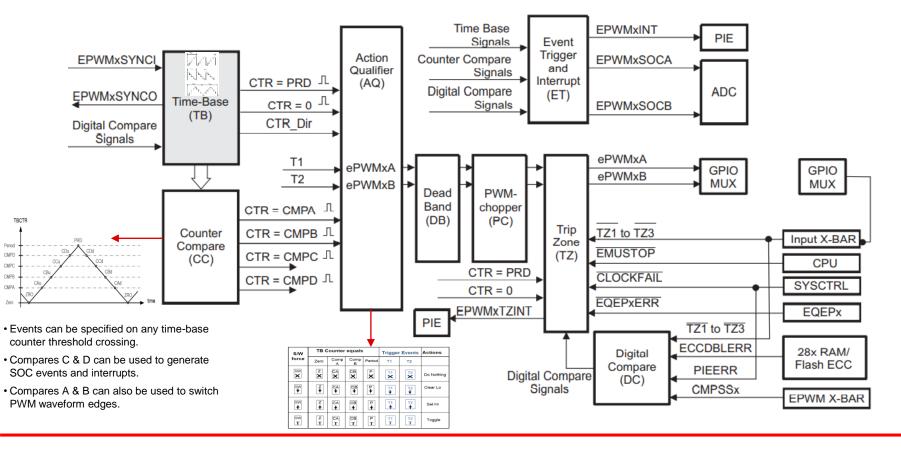

### C2000 Type-4 PWM module

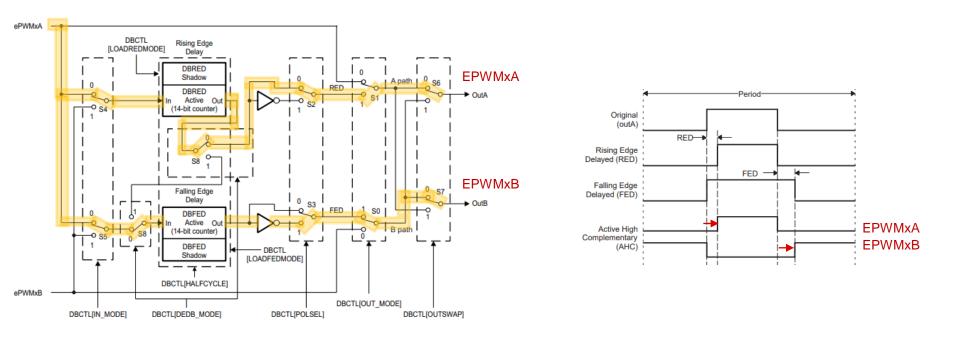

### C2000 dead-band submodule

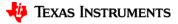

### ePWM phase shift and synchronization

- Phase is controlled between PWM modules by synchronizing time-base counters.

- In this example, PWM1 generates a SyncOut pulse on a CNT = Zero event. PWM2 receives the pulse at its SyncIn terminal and loads a phase offset of 200 into its TBCTR.

### Agenda

- EV chargers overview

- DC/DC: Dual active bridge

- C2000 PWM

- AC/DC: Vienna rectifier, ANPC PFC

- C2000 overview

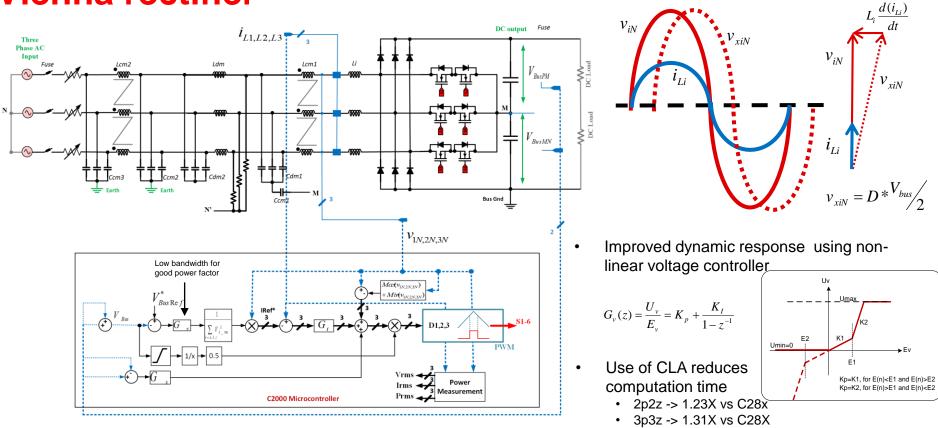

### **Vienna rectifier**

Reference design : Vienna Rectifier-Based, Three-Phase Power Factor Correction (PFC) TIDM-1000

16

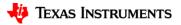

### **ANPC – Inverter / PFC**

Reference design : 11-kW, bidirectional, three-phase ANPC based on GaN reference design TIDA-010210

- Outer switches (Q1/Q4) need to turn OFF before turning OFF the inner switches (Q2/Q3)

- Positive cycle

- Q2 should never be turned off if Q1 is still ON

- Q1 should be turned OFF first and then Q2 after a defined delay

#### Negative cycle

- ✓ Q3 should never be turned off if Q4 is still ON

- Q4 should be turned OFF first and then Q3 after a defined delay

- Shutdown sequence need to be followed under trip conditions

- Software algorithm causes too much delay to provide in-time protection

- Use of external hardware circuits, like FPGA or CPLD increases system cost and development cost

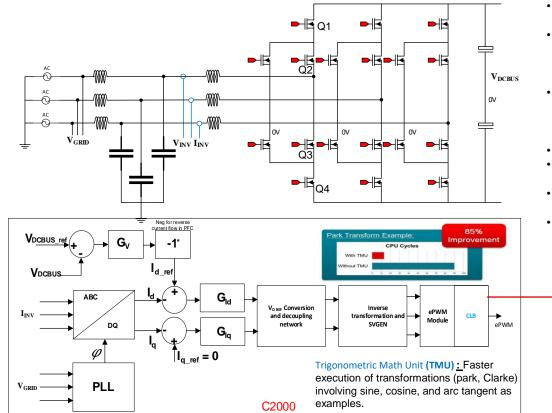

- Built-in Configurable logic block within C2000 lowers system cost by enabling shutdown sequence

#### Configurable logic block

### Agenda

- EV chargers overview

- DC/DC: Dual active bridge

- C2000 PWM and ADC

- AC/DC: Vienna rectifier, T Type PFC

- C2000 overview

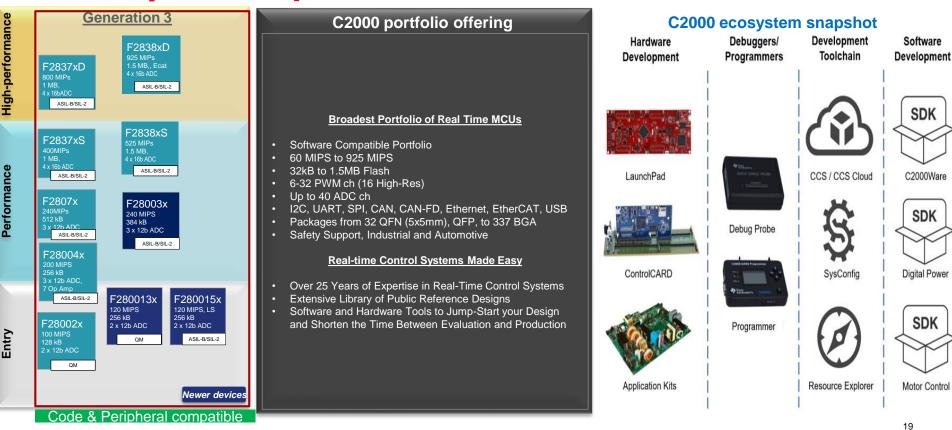

### C2000<sup>™</sup> product portfolio

### C2000<sup>™</sup> F28003x

#### Differentiation

Building on F28002x for High-Performance Power Control Applications Improved performance

- 120 MHz with CLA option

- 240 MIPS DSP Processing Power

- More Flash and RAM

- Better ADC Performance Effective throughput

#### Advanced actuation and design flexibility

Premium Type 4 ePWM modules with more instances and channels

#### Premium analog

- 8 Sigma Delta Decimation Filters (with separate Data and Comparator filters)

- 2 \* Buffered DAC 12-bit , +1 \* 12 bit ADC @ 3.45MSPS

#### **Rich digital options**

CAN-FD, +2 \* CLB tiles, +1 \* SCI

#### Safety

· ASIL-B/ SIL-2 safety enablers

#### Security

• AES, JTAG Lock & Secure boot

#### Perfect portfolio

- Pin-pin to F28002x 64-pin (non-Q) and 80-pin(non-Q) and almost compatible to 48-pin and 64-pin (Q)

- 100-pin option

# Tools

Experimenter's Kit

Part Number: TMDSCNCD280039C https://www.ti.com/tool/TMDSCNCD280039C LaunchPad

Part Number: LAUNCHXL-F280039C, 2Q22

Software

C2000Ware™ Software

Application SDKs

Package

#### http://www.ti.com/product/TMS320F280039C

| Sensing                                        | Processing                      | Actuation                                                                                  |  |

|------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------|--|

| ADC1: 12-bit, 4 MSPS,                          | C28x™ DSP core                  | 8x ePWM Modules<br>16x Outputs (8x High-Res)<br>Fault Trip Zones<br>2* 12-bit Buffered DAC |  |

| ADC2: 12-bit, 4 MSPS                           | 120 MHz                         |                                                                                            |  |

| ADC3: 12-bit, 4 MSPS                           | FPU, FastDIV, VCRC              |                                                                                            |  |

| 4x CMPSS : 12-bit DAC                          | TMU +NLPID                      |                                                                                            |  |

| 8 COMP, 8 digital filters                      | CLA core                        | Connectivity                                                                               |  |

| 8x Sigma Delta Channels<br>(2x Filters per ch) | 120 MHz, FPU                    | 2x SCI, 2x LIN/SCI                                                                         |  |

| Temperature Sensor                             | 6ch DMA                         | 2x I2C, 1x PMBus<br>2x SPI, 1x FSI-TX , 1x FSI-RX<br>1x CAN-FD, 1 CAN 2.0B                 |  |

| 2x eQEP                                        |                                 |                                                                                            |  |

| 3x eCAP , 1x HRCAP                             | BGCRC & HWBIST                  |                                                                                            |  |

|                                                | Memory                          | Power & Clocking                                                                           |  |

| Configurable Logic Block                       | 384 kB FLASH (3 bank) +ECC      | 2x 10 MHz OSC                                                                              |  |

| 4 Tiles                                        | 69 kB SRAM +ECC                 | 1.2V VREG                                                                                  |  |

|                                                | ROM with parity                 | POR/BOR Protection Debug                                                                   |  |

| System Modules                                 | Dual Security Zones             |                                                                                            |  |

| 3x 32-bit CPU Timers                           | Secure boot and JTAG lock       |                                                                                            |  |

| NMI Watchdog Timer                             | AES                             | cJTAG / Real-time JTAG                                                                     |  |

| 192 Interrupt PIE                              | Host Interface Controller (HIC) | ERAD                                                                                       |  |

| Functional Safety Compliant<br>Product |              |  |

|----------------------------------------|--------------|--|

| Target<br>Systematic<br>Capability     | ASIL-D/SIL-3 |  |

| Target<br>Diagnostic<br>Coverage (DC)  | ASIL-B/SIL-2 |  |

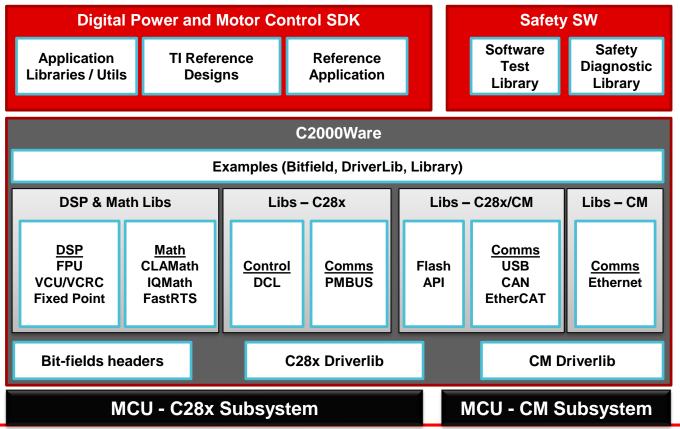

### **Software interfacing levels**

#### **Application-specific SDKs**

- Reference SW to get started for Digital Power and Motor Control

- Libraries and utilities to get started

#### Safety software (SW)

- Reference SW to implement Safety manual mechanisms

- Production ready STL for C28x and CLA diagnostic coverage

#### C2000Ware examples

- Examples for peripheral access using driver-lib or bit-field

- Examples for compute and communication libraries

#### C2000Ware libraries

Compute and Communication libraries for standard functions

#### C2000Ware driver lib / bit-field

Functional APIs for using a peripheral or accessing hardware registers

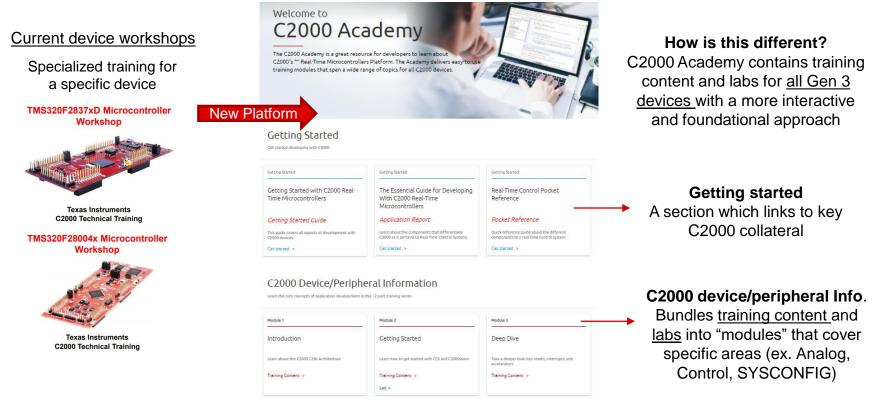

### **C2000 Academy: overview**

Dev.ti.com-> Resource Explorer -> Software -> C2000 Academy

22

### EMC FILTERING ON EV CHARGING STATION

Angelo Strati Italian Technical Team @ angelo.strati@we-online.com 334-6054571

WURTH ELEKTRONIK MORE THAN YOU EXPECT

### **The Würth Elektronik Group**

Würth Elektronik eiSos Electronic & Electromechanical Components

Würth Elektronik CBT Printed Circuit Boards

Würth Elektronik ICS Intelligent Power- and Control Systems

### **Free Technical Support**

- Possibility to agree on the presence of a FAE during the EMC tests in the laboratory

- Realization of free in-House seminars at your headquarters or in video-conference on different topics (EMC, ESD, DC / DC filtering, selection of inductors ...)

- Support in the selection of components for your application

- Sending of free samples for the prototyping phase and / or the EMC test phase

- Possibility to request on-site presence for project support

#### Agenda

- EV Charging Station with C2000

- Sources Of Interference

- Filtering Components

### **EV Charging Station Scheme**

### **Sources Of Interference**

- PWM Drive

- Control Logic and Oscillator

- Interfaces

- Switching Regulator

- Layout

- Wiring

### **Wired Interference – Conducted Emission**

- Cause of the interference voltage of 150kHz ... 30MHz:

- Ripple current on the supply side

- Rise/fall time controlled by gate drive

- Interference current via parasitic coupling capacitances to ground (common mode)

- The unbalanced voltage sampled per phase contains symmetrical and asymmetrical components.

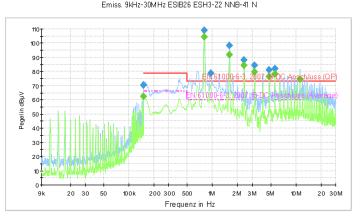

- Limit value for the asymmetrical interference voltage, e.g. according to EN 61000-6-3

### **Noise Emission – Radiated Emission**

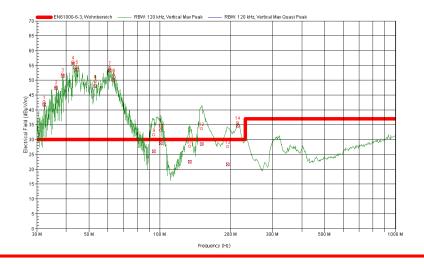

- Cause for the interference field strength of 30MHz ... 1 (6) GHz:

- Noise current on conductor tracks or loops

- Noise current on conductive housings

- Interference current on lines connected to interfaces

- Limit value for the radio interference field strength e.g. according to EN 61000-6-3

### **Overwiev Sources Of Interference**

| Type of Fault                  | Dominant Source                                                                                      | Frequency Range | Radiated or<br>Conducted  |

|--------------------------------|------------------------------------------------------------------------------------------------------|-----------------|---------------------------|

| Low Frequency<br>Range         | Fundamental and<br>harmonics of the<br>controller switching<br>frequency                             | 10kHz to 30MHz  | Conducted                 |

| Broadband<br>Interference      | dI / dt and dU / dt of<br>the FET (silicon)<br>switching edges and<br>parasitic resonant<br>circuits | 30MHz to 200MHz | Conducted and<br>Radiated |

| High Frequency<br>interference | Reverse Recovery of<br>Schottky Diodes                                                               | Over 200MHz     | Radiated                  |

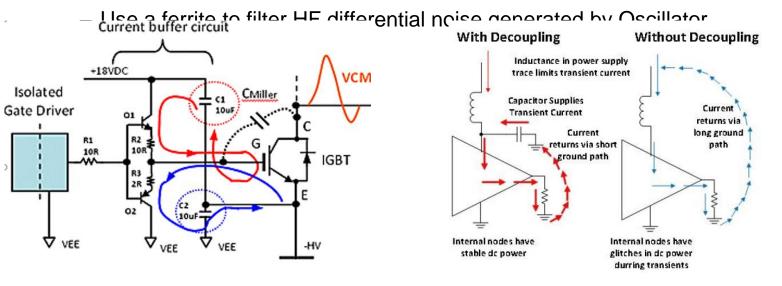

### **Differential Mode Interference: Filtering**

- Minimizing the differential mode interferers by:

- Placing a RF decoupling "C" close to the switching node

- Keep high ΔI / Δt loops (loop antennas) compact → Minimization of H-fields

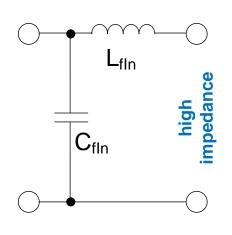

### **Differential Mode Interference: Filtering**

- DM Filtering:

- Input LC Filter to attenuate PWM signals (High repetitive pulse)

- Rise/Time controlled by Gate Drive

- Place the correct way: input impedance of the transducer is very low, normally mainly dominated by the one or two capacitors

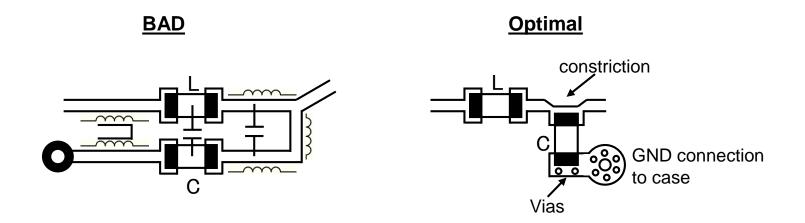

### Layout Suggestions On Drive Board: GND Reference For Filter

- Constriction reduces reflections (VSWR) in gigahertz range

- Right angle arrangement reduces capacitive coupling

- Vias and direct conductive board mounting enable low-impedance ground connection

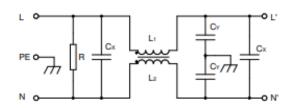

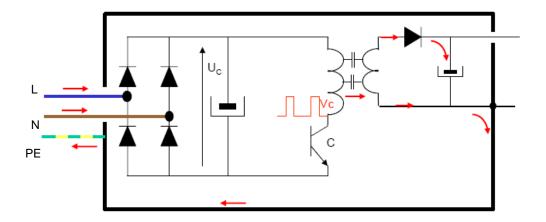

### **Common Mode Interference: Common Mode Choke**

- Large common mode current paths due to the heat sink formation of HF capacitance

- These leads to problems with the Conducted & Radiated Measurement!

- Use Common Mode Choke and X or Y caps

FET : fsw to 20MHz

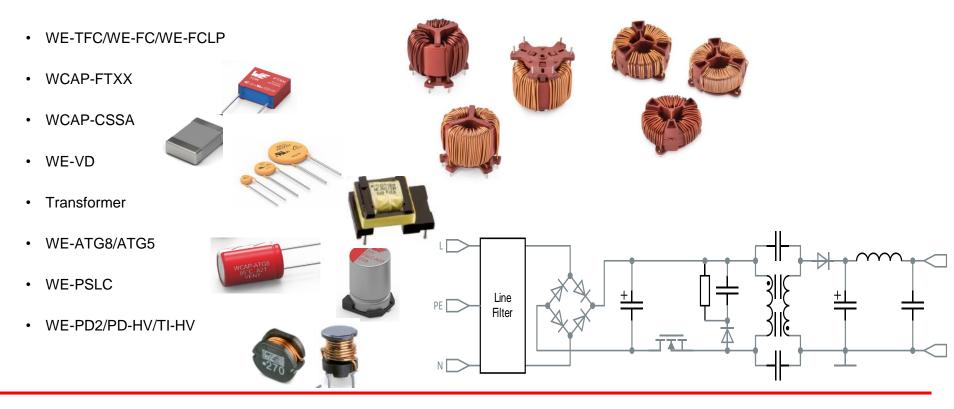

#### 20.01.2023 Aux ACDC converter, what can we provide?

Converts the AC input to power up all the DC logic inside

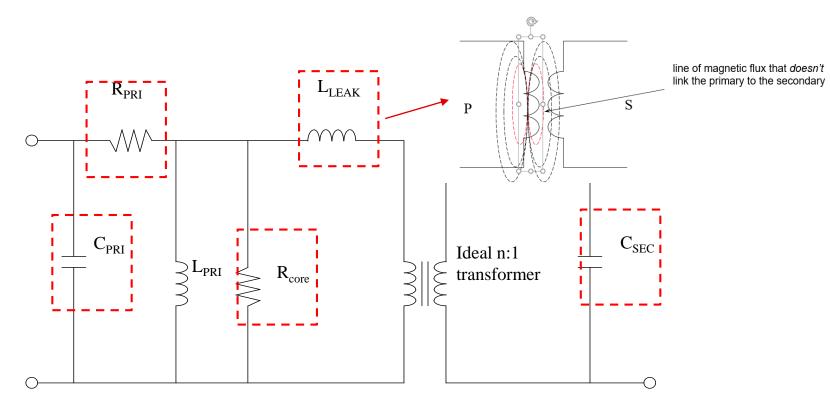

#### **Parasitics – Transformer Standard Model**

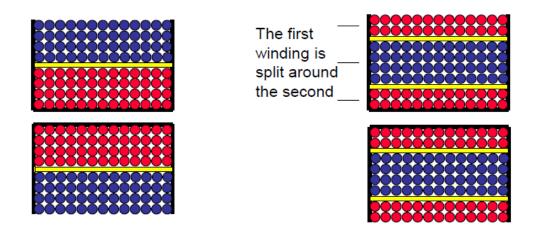

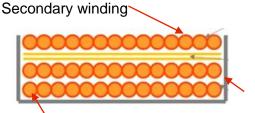

# Leakage Inductance – Good Construction

To improve the coupling between the windings we can sandwich the first winding around the second. This reduces the average distance between the windings and results in 1/4<sup>th</sup> the original value of leakage inductance – at the expense of more winding labor.

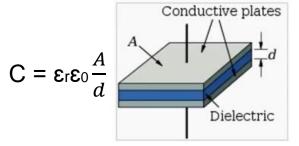

### **Transformer for EMC : C**ww

- Noise couples through the transformer via C<sub>ww</sub>

- Noise seeks path to primary circuit

- Without path, noise may become conducted emissions

### **Reducing InterWinding Capacitance**

How can we reduce the inter-winding capacitance

P-S boundary (usually layers of tape)

Primary winding

- Multi-section or Narrow bobbin

- · Lots of tapes and increase the insulation thickness on wire

- This will result in increasing the leakage inductance (we have to use Snubber to control it)

- Possibly reducing the electric constants using for example low dielectric varnishes or potting compounds on wires (Does not affect the leakage inductance)

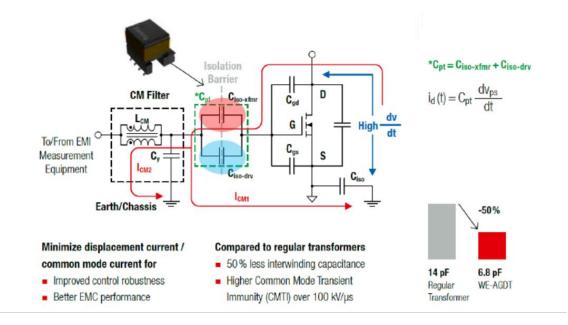

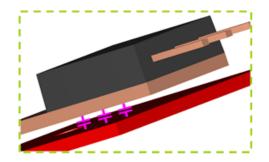

## Gate Drive Trasformer for SIC-

#### Isolation Barrier Parasitic Capacitance: Common-mode Transient Immunity (CMTI) and EMI Performance

Common-mode Transient Immunity (CMTI) (measured in kV/us or V/ns), is an indication of the maximum dV/dt which can be tolerated across the isolation barrier before malfunction of the gate driver system occurs, due to excessive distortion of the gate drive control signals.

- SiC-MOSFETs switch extremely fast, helping to increase efficiency and reduce system size and cost.

- Fast switching speed causes high dV/dt to appear across the isolation barrier parasitic capacitance (Gate driver IC and auxiliary supply transformer).

- Common-mode displacement currents are generated.

- A lower parasitic capacitance reduces these displacement currents, helping to achieve a higher CMTI rating and better EMI performance.

- It is critical to minimize the transformer interwinding capacitance in fast-switching SiC-MOSFET gate drive applications.