## DESIGN, LAYOUT & SIMULATION OF 3-PHASE ACDC FILTERS

Andreas Nadler Field Application Engineer WURTH ELEKTRONIK MORE THAN YOU EXPECT

### 3-Phase Filter Design

- Sources of interference

- Components for filtering

- Filter Design

- Y-Cap placement, leakage current and PE connection style

- Calculation and simulation

- Measurements of interference suppression

- Varistor calculation and placement

# FILTER DESIGN 1-PHASE & DCDC

## Related Appnote: ANP015 Coming 2025: ANP137 (3-Phase)

#### **Application Note**

#### 1-Phasen Netzfilter Design

#### ANP015b // Andreas Nadler

#### 1 Einleitung

Ziel dieser Appnote ist es, dem Leser so kompakt wie möglich einen umfassenden Überblick der notwendigen Schritte hin zum passend dimensionierten Netzfilter zu geben. Hierbei wird ein diskreter 1-Stufen mit einem diskreten 2-Stufen Netzfilter mittels Berechnung, Simulation und Messung verglichen. Im weiteren Verlauf werden die unterschiedlichen Kernmaterialien von Stromkompensierten Drosseln und deren Eigenschaften erläutert. Zudem widmet sich diese Appnote der Berechnung von: Varistoren, Leckströmen und Entladewiderständen. Diese Appnote setzt gewisse Grundkenntnisse von passiven Bauelementen, Filtern sowie EMV Messtechniken voraus.

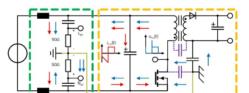

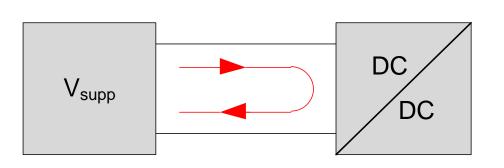

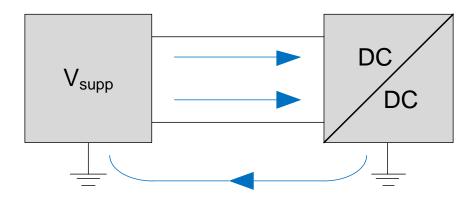

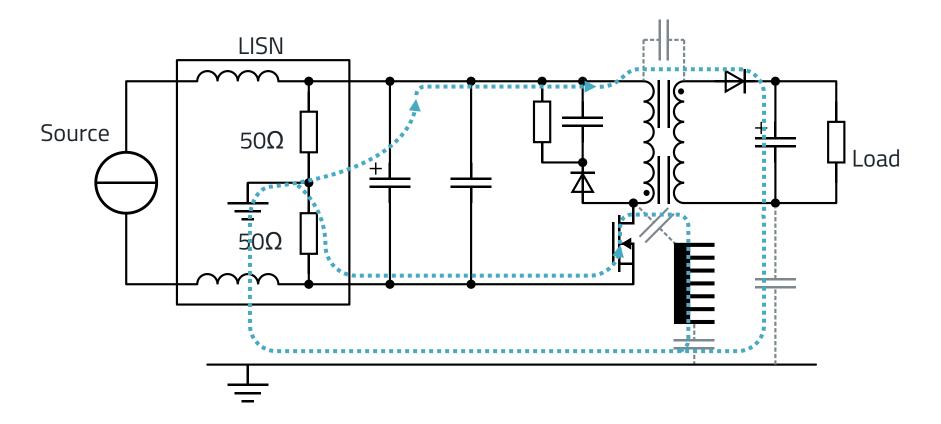

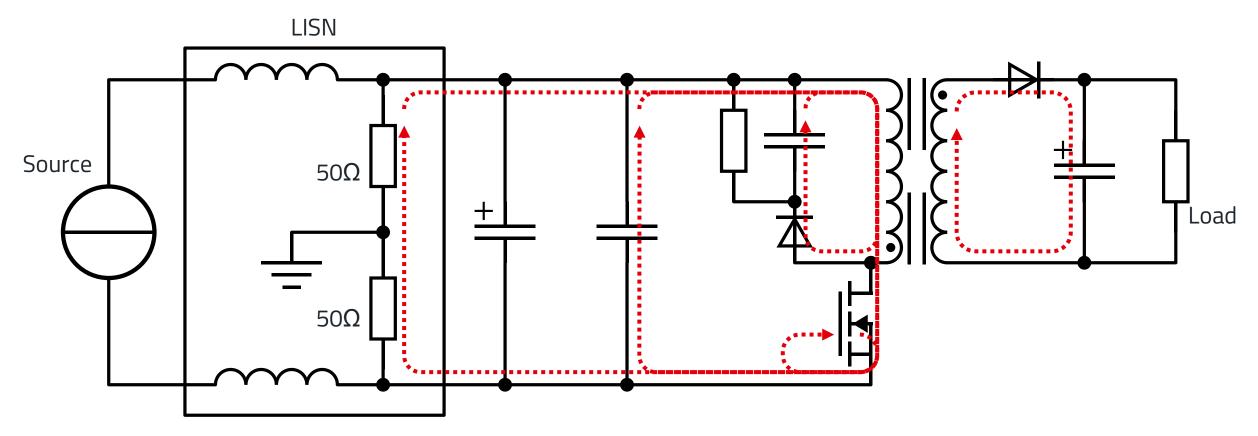

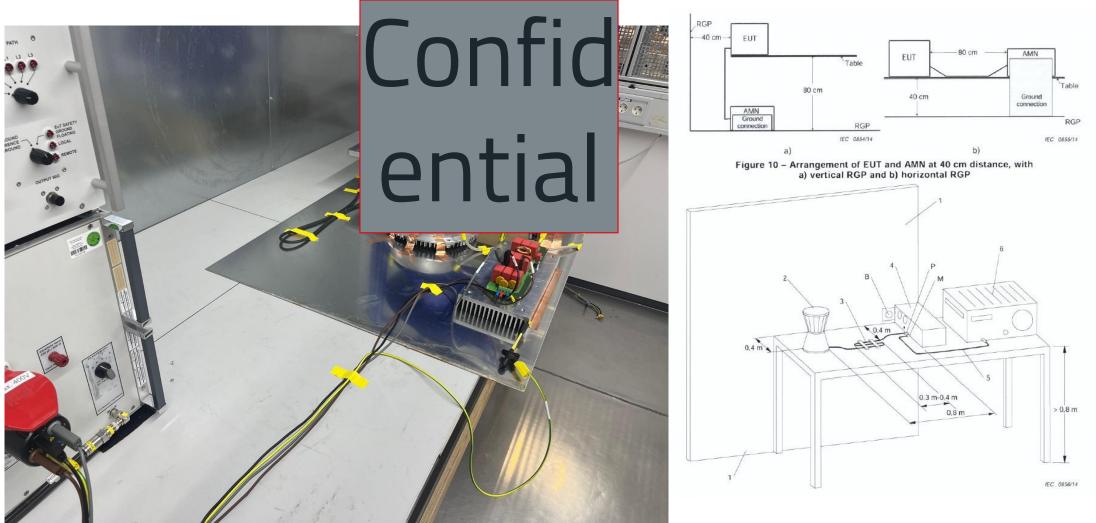

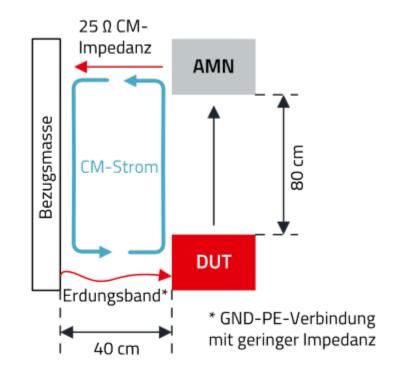

#### 2 Precompliance Messaufbau

Grundlegend ist zwischen zwei verschiedenen Störstrompfaden zu unterschieden: Gleichtakt (Common Mode, CM) sowie Gegentakt (Differential Mode, DM). In einer EMV Abnahmemessung werden grundsätzlich beide Störstrompfade gleichzeitig gemessen. Um einen Netzfilter auszulegen ist es vorteilhaft im Vorfeld beide Ströpfade, CM und DM, messen zu können. Dazu wird eine LISN (Line Impedance Stabilization Network) benötigt, bei der die zwei Messausgänge gleichzeitig nutzbar sind. In der LISN sind zwei  $50\Omega$  Messwiderstände verbaut. In der DM Messung liegen diese in Reihe ( $100\Omega$ ), wohingegen sie in der CM Messung als parallel zu betrachten sind ( $25\Omega$ ). Das Blockschaltbild in Abbildung 1 zeigt die DM- und CM-Störstrompfade zwischen einem Sperrwandler (Störquelle) und der LISN

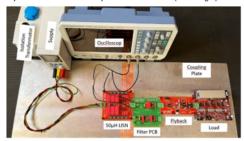

Für die Precompliance Messung wird ein Rohde&Schwarz RTA4004 mit 500MHz analoger Bandbreite in Kombination mit der Desktop Software *R&S EMI Debug Tool* und einer CISPR16 LISN (Eigenbau) verwendet (Aufbau in Abbildung 2).

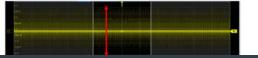

Zu beachten ist, dass die maximale vertikale Auflösung der Messeingänge des Oszilloskops optimal ausgenutzt wird, der Amplitudenmessbereich aber auch nicht übersteuert wird. Hat die erfasste Störspannung im Zeitbereich z.B. einen Peak to Peak Pegel von 85mV, so sollte die vertikale Einstellung auf einen Endwert von 100mV gesetzt werden, um die Empfindlichkeit des Oszilloskops maximal zu nutzen (Abbildung 3).

Abb. 2: Precompliance Messaufbau mit Koppelplatte, LISN, DUT, Trenntrafo & Oszilloskop

# SOURCE OF INTERFERENCE

## **Differntial Mode & Common Mode**

**Differential Mode**

## CM & DM comparisson

- Differential mode currents

- <u>Current path as in circuit diagram</u>

- Easy to follow paths

- Return current path very close

- <u>Relatively large currents</u>

- <u>Filtering with LC , π , T topologies</u>

- <u>dl / dt is dominant cause</u>

- <u>Conducted EMI problem</u>

- <u>Common-mode currents</u>

- <u>Unexpected current path</u>

- <u>Current flows via parasitic paths</u>

- <u>Return current path very large</u>

- <u>Relatively small currents (μA)</u>

- Filtering with CMC and Y-caps

- <u>dU / dt is dominant cause</u>

- <u>Radiated & conducted EMI problem</u>

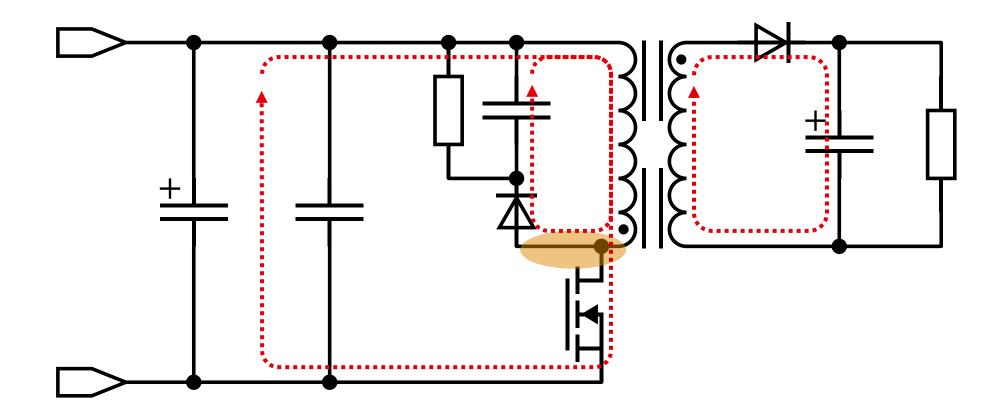

## Introduction – Flyback Converter

Hot Node and Critical Loops

## Introduction - Capacitive Coupling in a Flyback Converter

Common mode current paths

High du/dt common mode currents through parasitic capacitances (electric dipole and monopole antennas)

## Introduction - Inductive Coupling in a Flyback Converter

Differential mode current paths

Inductive coupling caused by high di/dt differential mode currents (magnetic loop antennas)

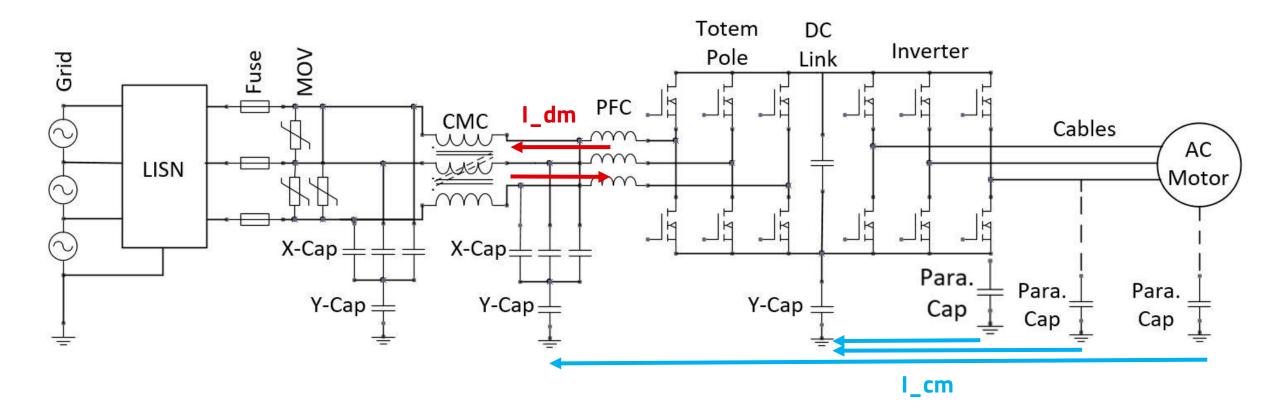

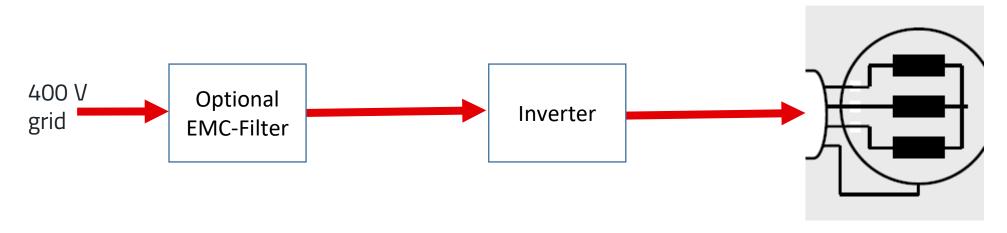

## Sources of interference 3 phase system

Typical application: inverter for industrial drives

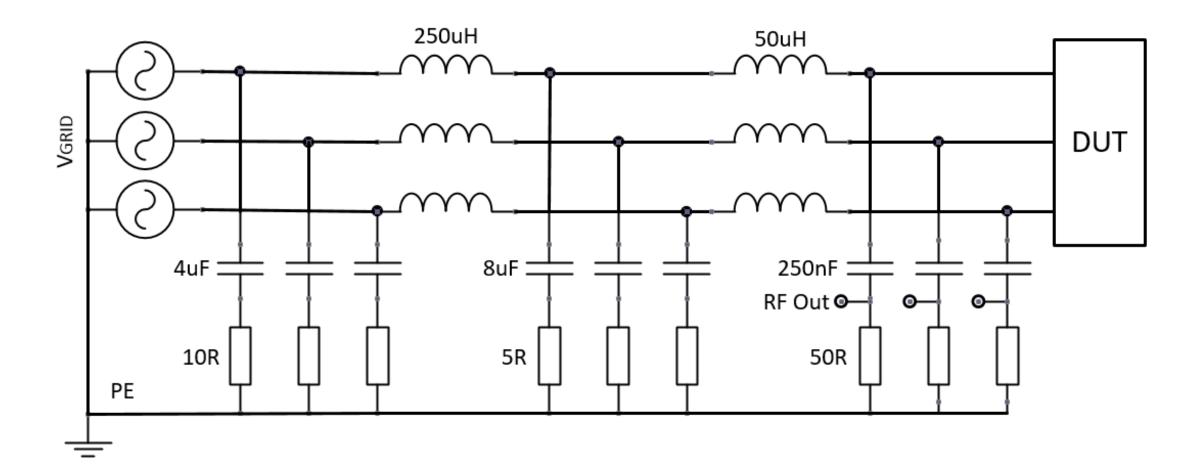

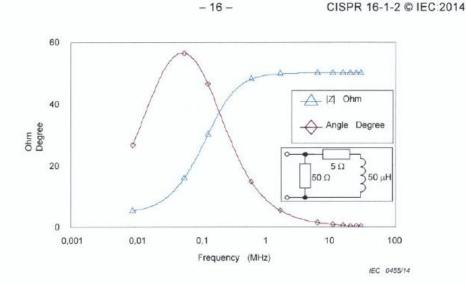

## **3-Phase LISN**

CISPR 16 LISN

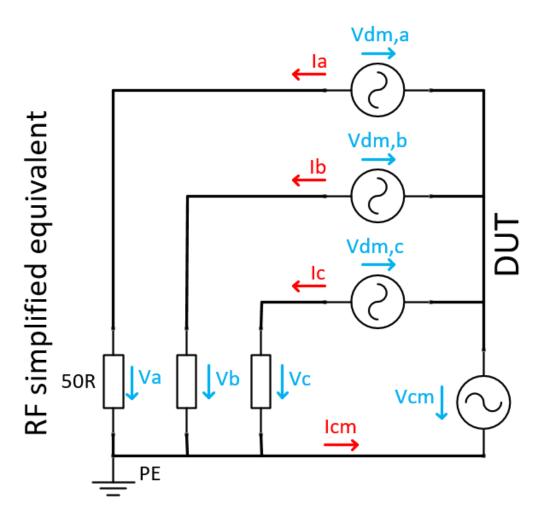

## LISN / DUT

Simplified RF model

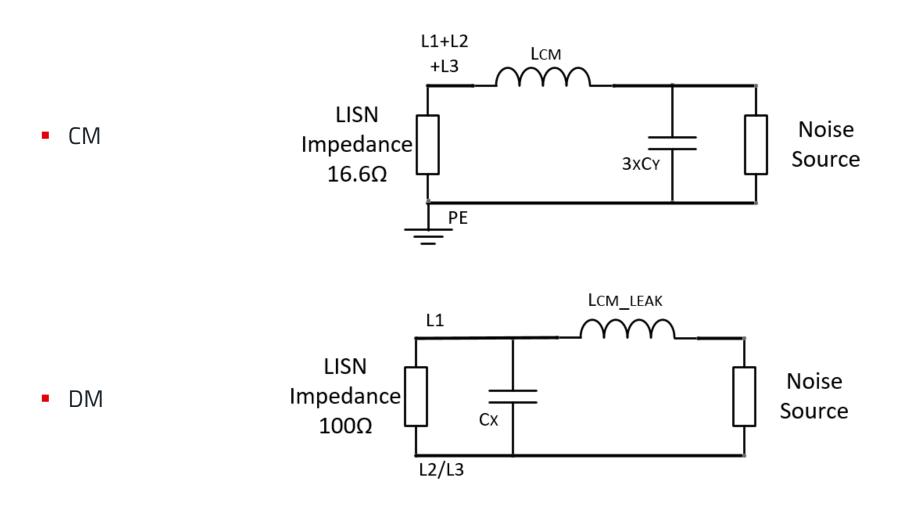

•

$$R_{CM} = \frac{R_{LISN}}{3} = \frac{50\Omega}{3} = 16.67\Omega$$

- $R_{DM} = R_{LISN} \cdot 2 = 50\Omega \cdot 2 = 100\Omega$

- $I_{CM} = I_a + I_b + I_c$

- $I_{DM,a} + I_{DM,b} + I_{DM,c} = 0$

•

$$V_{CM} = I_{CM} \cdot \frac{R_{LISN}}{3} = \frac{V_a + V_b + V_c}{3}$$

•

$$V_{DM,a} = V_a - V_{CM} = \frac{2 \cdot V_a}{3} \cdot \frac{V_b}{3} \cdot \frac{V_c}{3}$$

## <u>COMPONENTS</u>

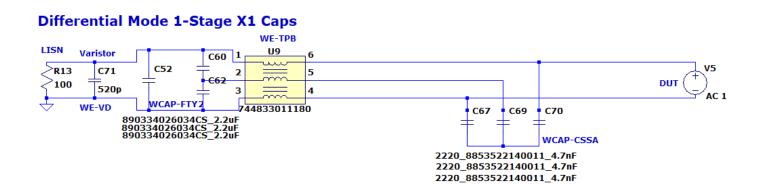

X1 / Y2 Caps

### MKP Film(Prototyp Status)

- WCAP-FTY2

- Pitch 10 37,5mm

- Vr: 330VAC

- 1nF 1μF

- X1 + Y2 class

### MLCC X7R / NPO

■ 33pF – 4.7nF

WCAP-CSSA

1808 – 2220

• Vr: 250VAC

- X1 + Y2 class

- -55°C to +125°C

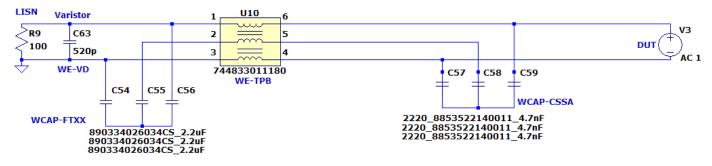

## X2 Caps

#### МКР

- WCAP-FTXX / FTX2

- Pitch: 7.5 37.5mm

- Vr: 310VAC / 275VAC

- 5.6nF 6.8µF

- -40°C to +105°C

МКР

- WCAP-FTXH

- Pitch: 15 37.5mm

- Vr: 310VAC

- 33nF 10μF

- -40°C to +110°C

- THB rated: 1000h @ 85°C + 85% humidity

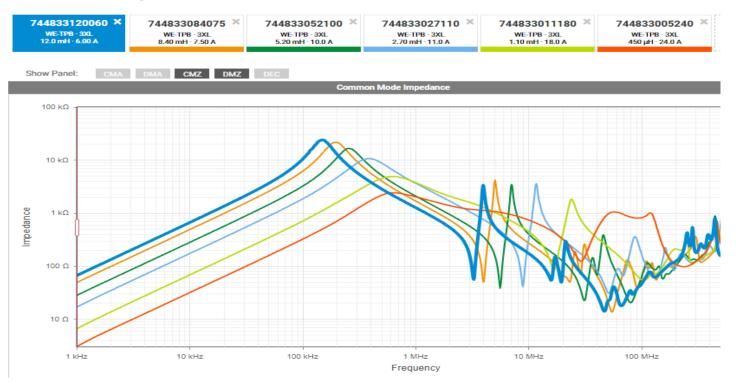

## <u>CMC<sup>´</sup>s</u>

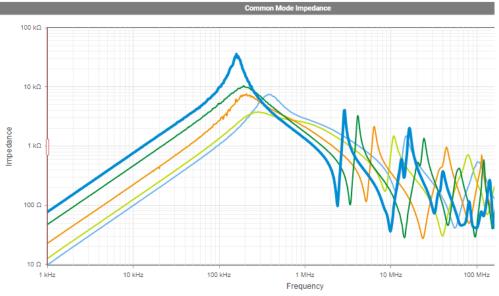

3-phase 500V - WE-TPB – Ø47mm

- **MnZn** core material / -40°C to +125°C

- 1kHz to 2MHz effective frequency range

- Up to 24A

- 0,52mH to 12mH

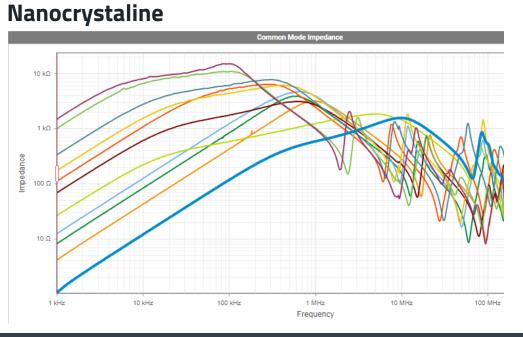

## <u>CMC<sup>´</sup>s</u>

3-phase 760V – WE-TPBHV – Ø70mm

- MnZn & Nanocrystaline core materials / -40°C to +125°C

- 1kHz to 20MHz effective frequency range

- Up to 46A

- 0,2mH to 208mH

### MnZn

## **Surge Protection Varistors**

WE-VD

- 5 20mm Ø THT

- Vrms: 14V 1000V

- Imax: 100A 10000A

- -40°C to 85°C

- UL, IEC & VDE certified

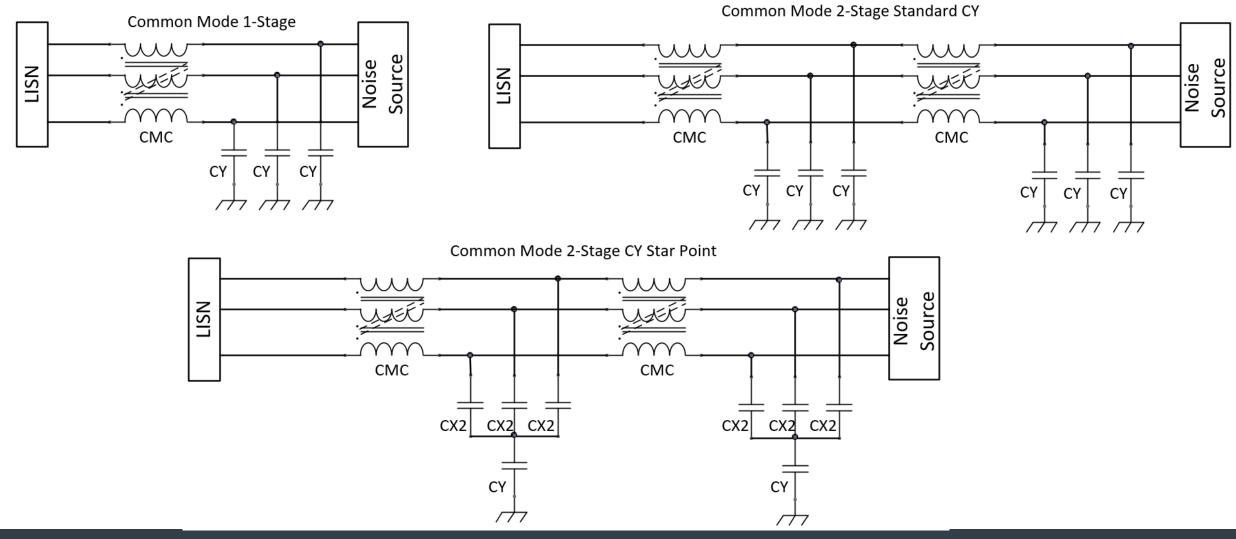

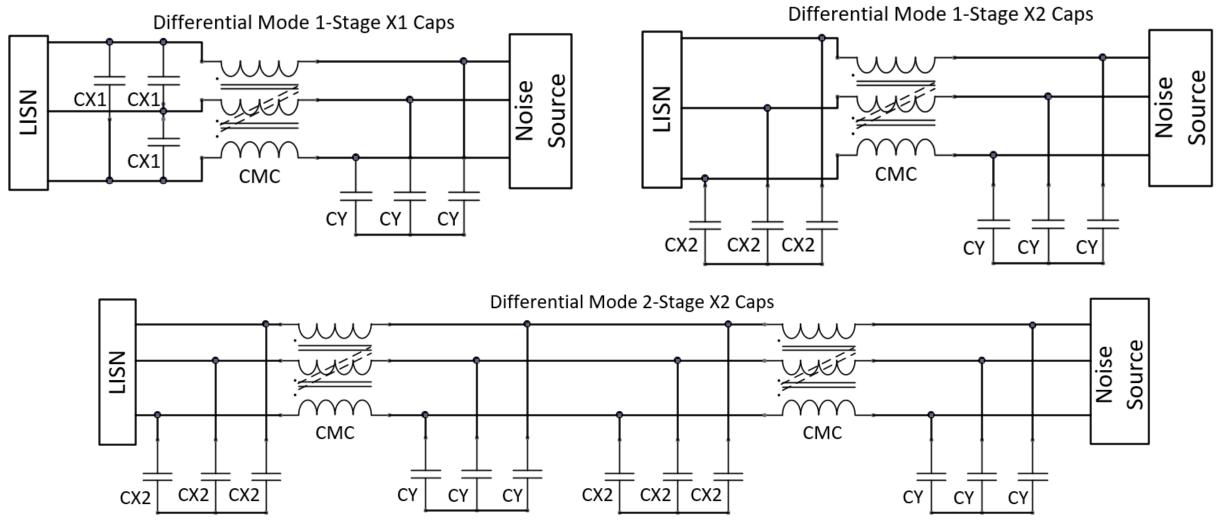

# POSSIBLE FILTER STRUCTURES

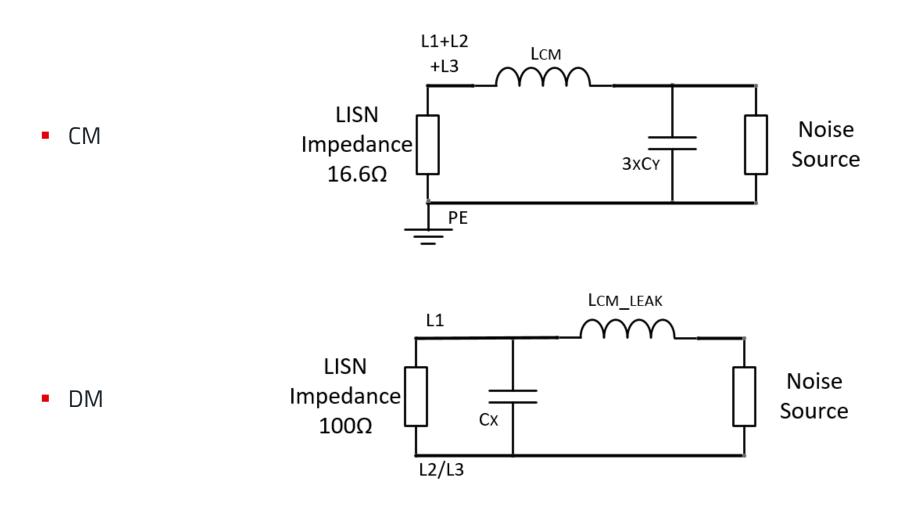

## CM & DM Filter Equivalent

Effective LISN Impedance and Component Arrangement

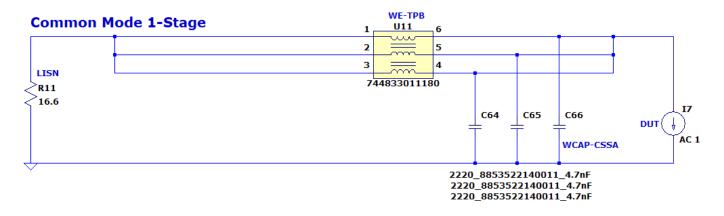

## Possible Filter Structures Common Mode

### Main CMC Inductance + Y-Caps

## **Possible Filter Structures Differential Mode**

### CMC Stray Inductance + X-Caps

# SIMULATION OF DIFFERENT FILTER STRUCTURES

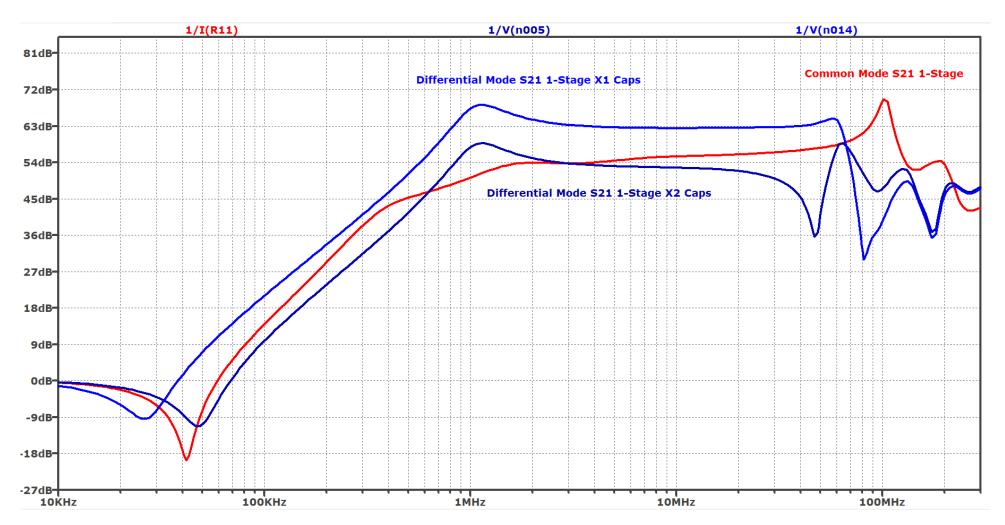

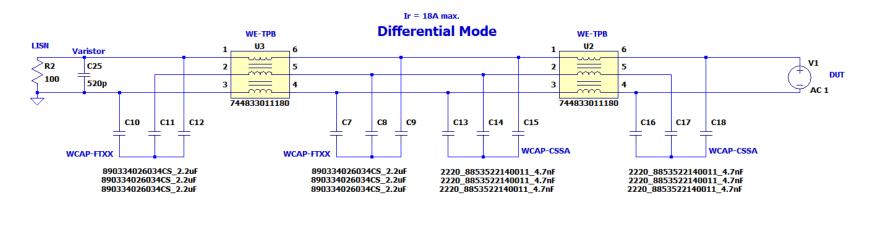

## **LT Spice Simulation**

1-stage filter for 400V / 18A / 11kW

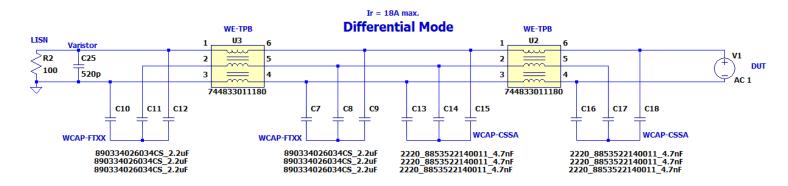

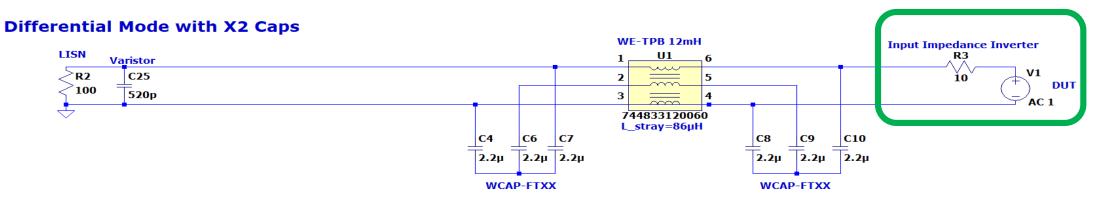

#### Differential Mode 1-Stage X2 Caps

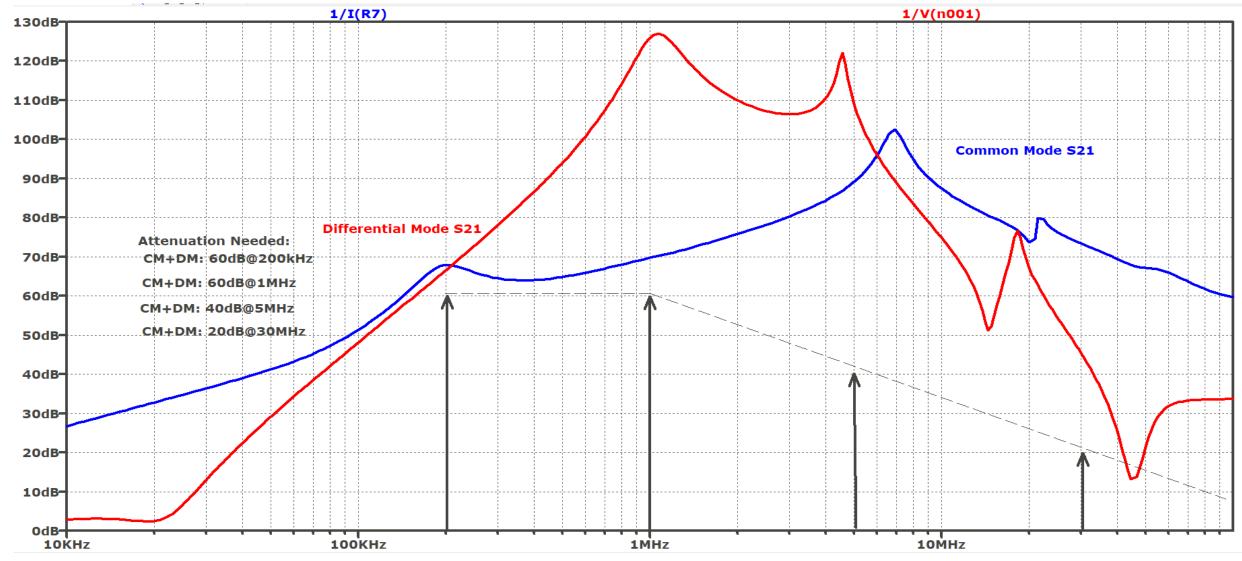

## **LT Spice Simulation Insertion Loss**

1-stage filter for 400V / 18A / 11kW

26 26.07.2024

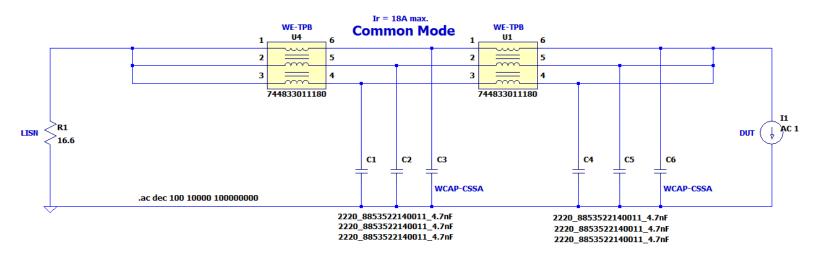

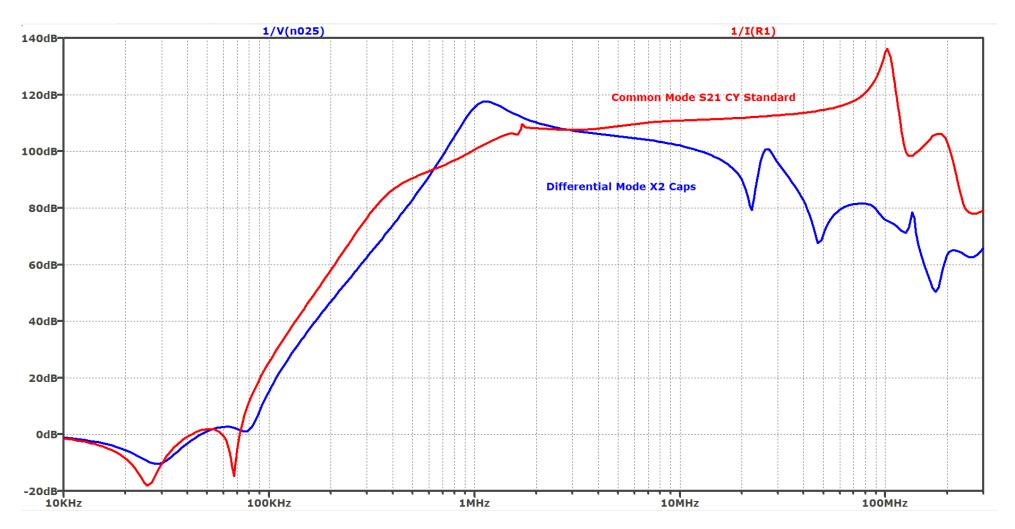

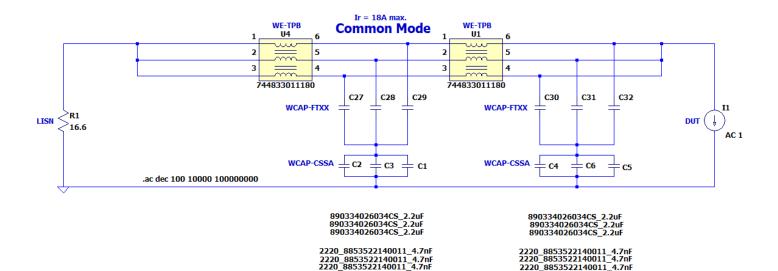

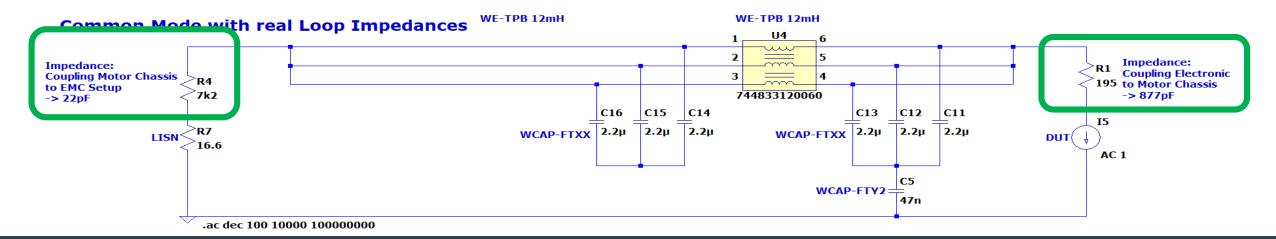

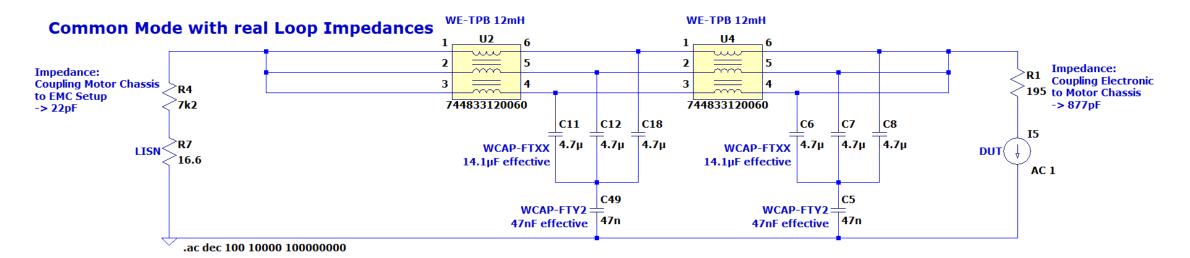

## **LT Spice Simulation**

2-stage filter for 400V / 18A / 11kW / Standard CY

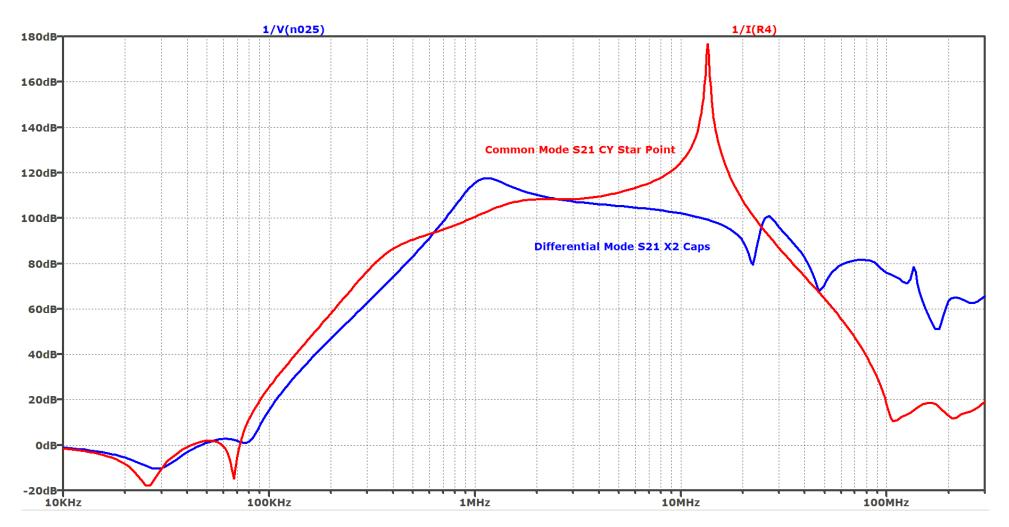

## LT Spice Simulation Insertion Loss S21

2-stage filter for 400V / 18A / 11kW / Standard CY

## **LT Spice Simulation**

2-stage filter for 400V / 18A / 11kW  $\rightarrow$  CY - Star Connection

## LT Spice Simulation Insertion Loss S21

26.07.2024

30

2-stage filter for 400V / 18A / 11kW  $\rightarrow$  Y-Cap Star Connection 3x4.7nF= 14.1nF

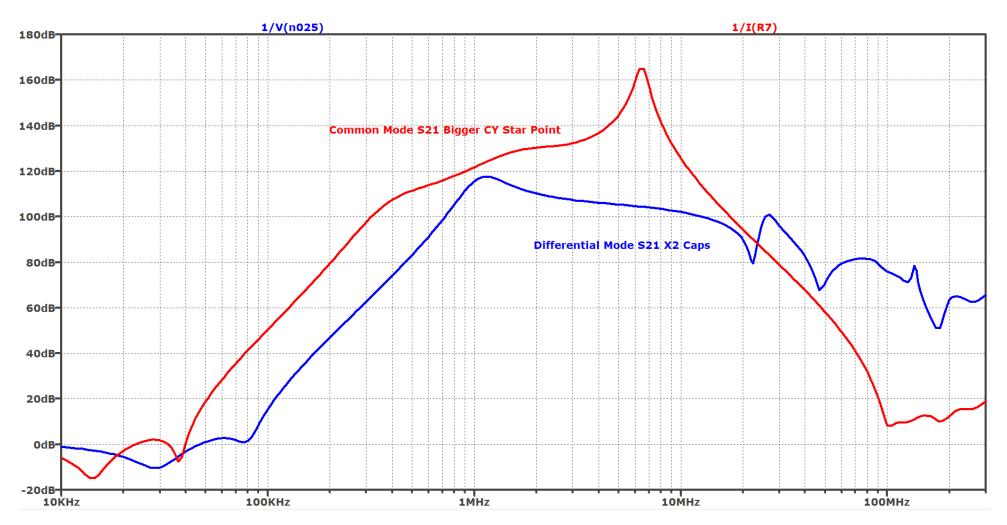

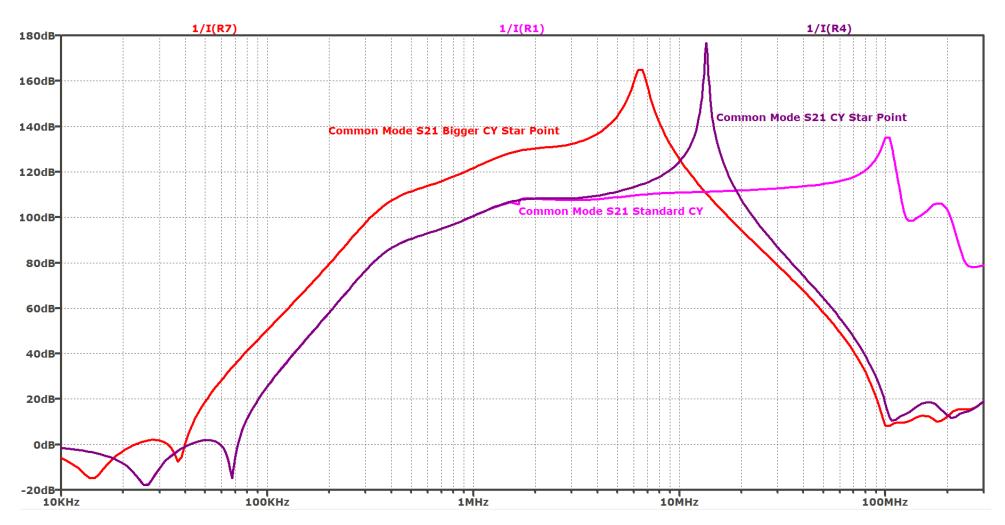

## LT Spice Simulation Insertion Loss S21

2-stage filter for 400V / 18A / 11kW  $\rightarrow$  Y-Cap Star Connection **bigger** Y-Cap (47nF)

## ST Spice Simulation Insertion Loss S21

Compare all 3 Common Mode Configurations

# MEASUREMENTS IN THE LAB

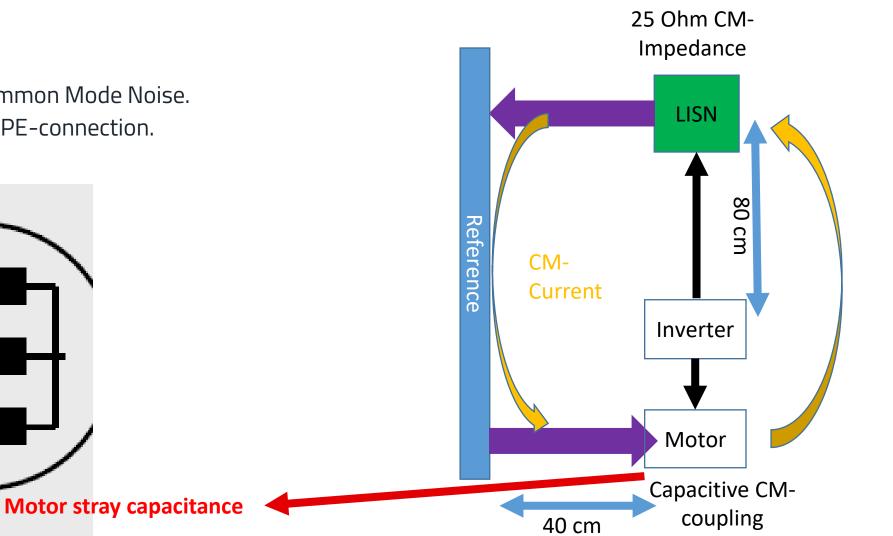

Motor drive system

3 kW; 5 A motor current.

### Conducted emission testing

## Test Setup

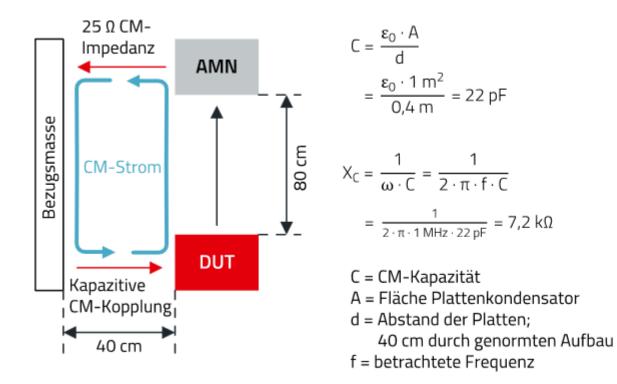

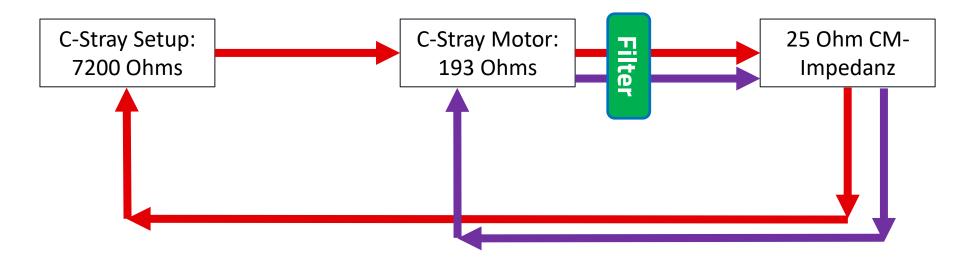

Conducted emissions testing – basic idea CM-coupling

## <u>Test setup</u>

Detailed coupling

- Motor is noise source for Common Mode Noise.

- Coupling over the air or over PE-connection.

#### Motor stray capacitance

Measurement with LCR-meter

- Motor stray capacitance: 877 pF @ 2 MHz.

- Winding to chassis.

Cp- ...

AUTO Ø V

BIAS Ø V MEAS TIME LONG

877.2240 pF

.6167

MEAS DISPLAY>

EVEL

GAUSS

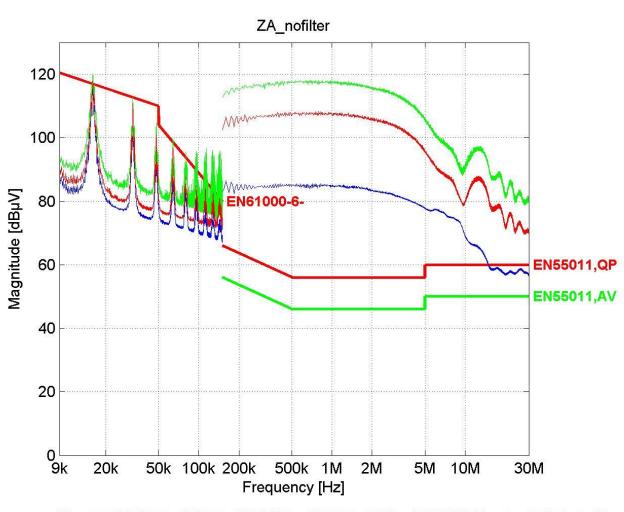

No filter

Scan1: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 10.0 s, QP, TDF Standard, Att AutodB, Scan2: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 10.0 s, CAV, TDF Standard, Att AutodB, Scan3: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, MaxPeak, TDF Standard, Att AutodB, Scan4: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 10.0 s, MaxPeak, TDF Standard, Att AutodB, Scan5: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, QP, TDF Standard, Att AutodB, Scan5: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, QP, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB,

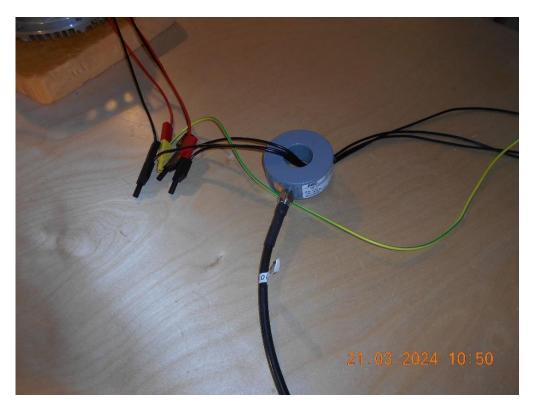

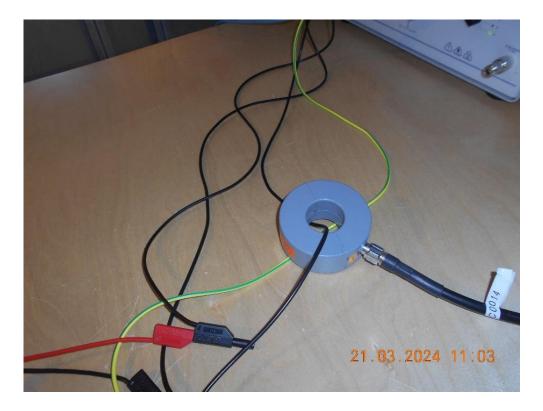

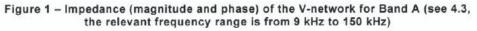

#### <u>Common Mode vs Differential Mode</u>

Current probe setup

• Common mode on all 3 lines:

Differential mode + common mode on single line

### **Common Mode vs Differential Mode**

Current probe setup

- Current probe:

- Linear performance starting at 10 kHz.

- Note: LISN is linear at 50 Ohms starting at MHz range!

- LISN linear starting at 1 MHz.

### <u>Common Mode vs Differential Mode</u>

DUT with PE / Earth connection

- Green = common mode current on all 3 lines

- Yellow = differential mode current + common mode current on a single line

DM noise dominant below 50 kHz!

11:18:13 AM 03/21/2024

#### **Filter Calculation**

Common mode loop

- Attenuation earthed 60 dB required -> 1000 times reduction of the noise current.

- 218 Ohms loop impedance -> 218 000 Ohms Filter impedance if only CMC is used...

• Complexe filter calculation or simulation possible, when impedance system is known.

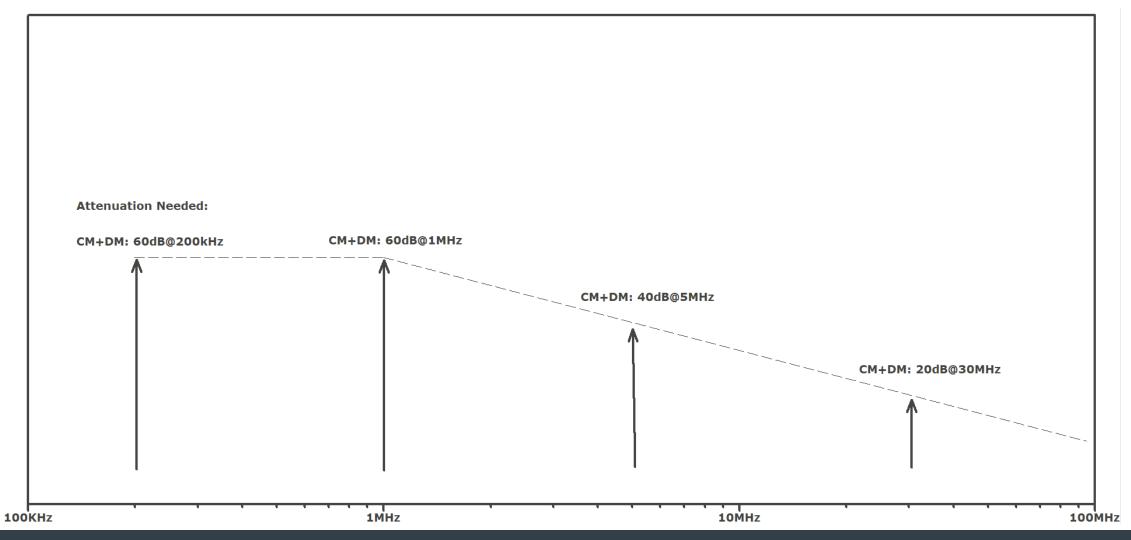

#### **Requiered Filter Attenuation**

DM & CM

### CM & DM Filter Equivalent

Effective LISN impedance and component arrangement

### CM & DM Filter Equivalent

Effective Cx and Cy in 3 phase systems

- Cx between each phase:

- $Cx_{effective} = \left(\frac{1}{CX1} + \frac{1}{CX2}\right)^{-1}$

•

$$Cy_{effective} = (\frac{1}{CX1 + CX2 + CX3} + \frac{1}{CY})^{-1}$$

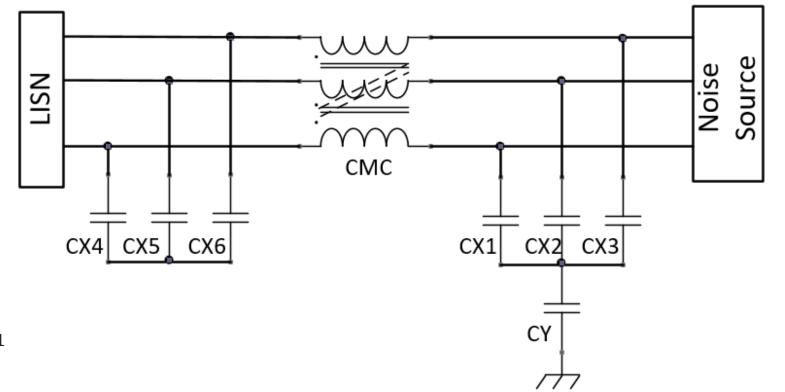

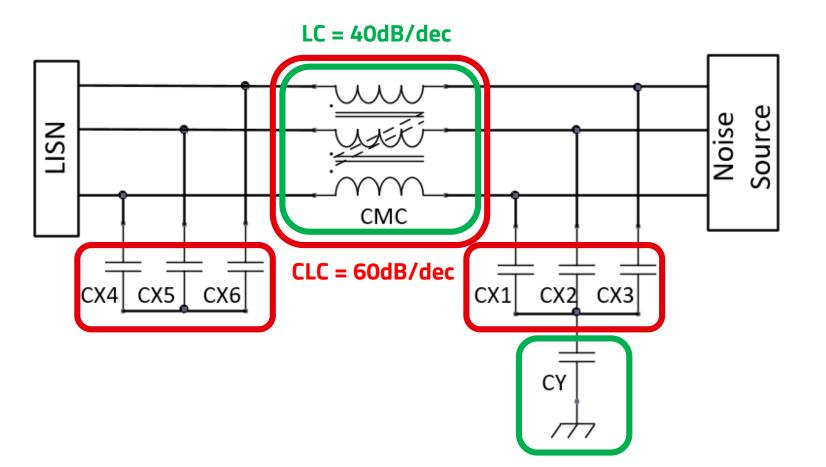

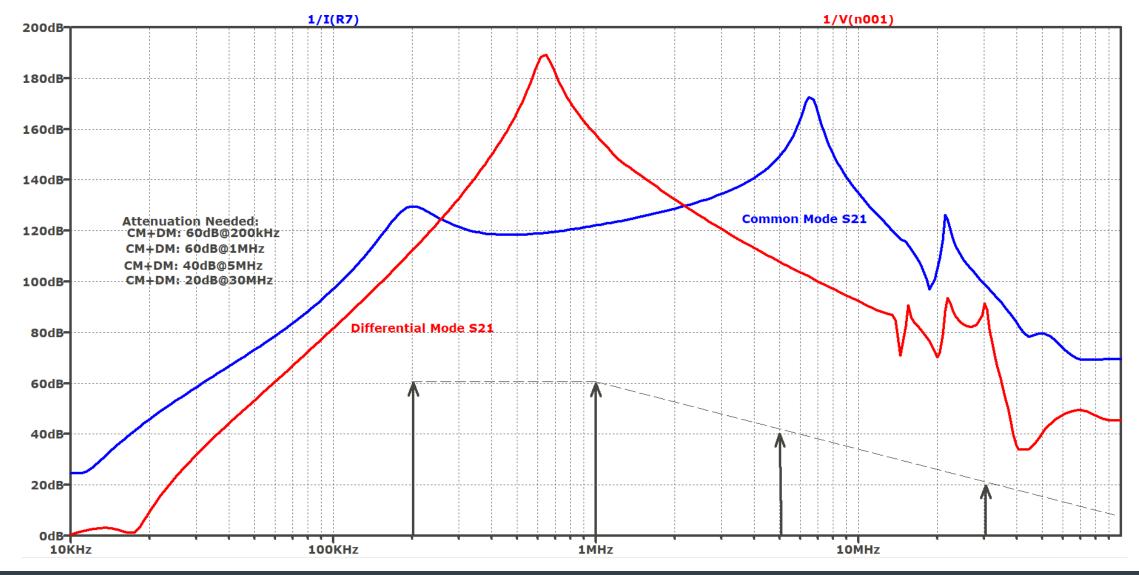

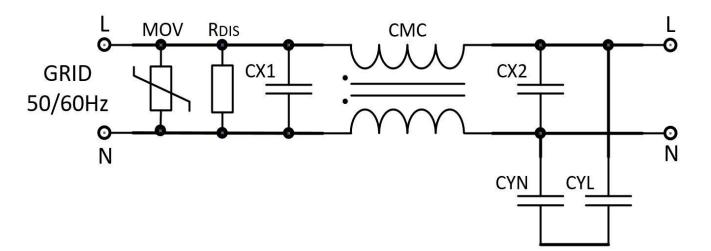

### Chosen Filter Structure for DUT 150kHz to 30MHz

"CLC" for  $\ensuremath{\text{DM}}$  and "LC" for  $\ensuremath{\text{CM}}$

- **DM** filter provides 60dB/dec

- Leakage of CMC + X-Caps

- **CM** filter provides 40dB/dec

- CMC main inductance + Y-Cap

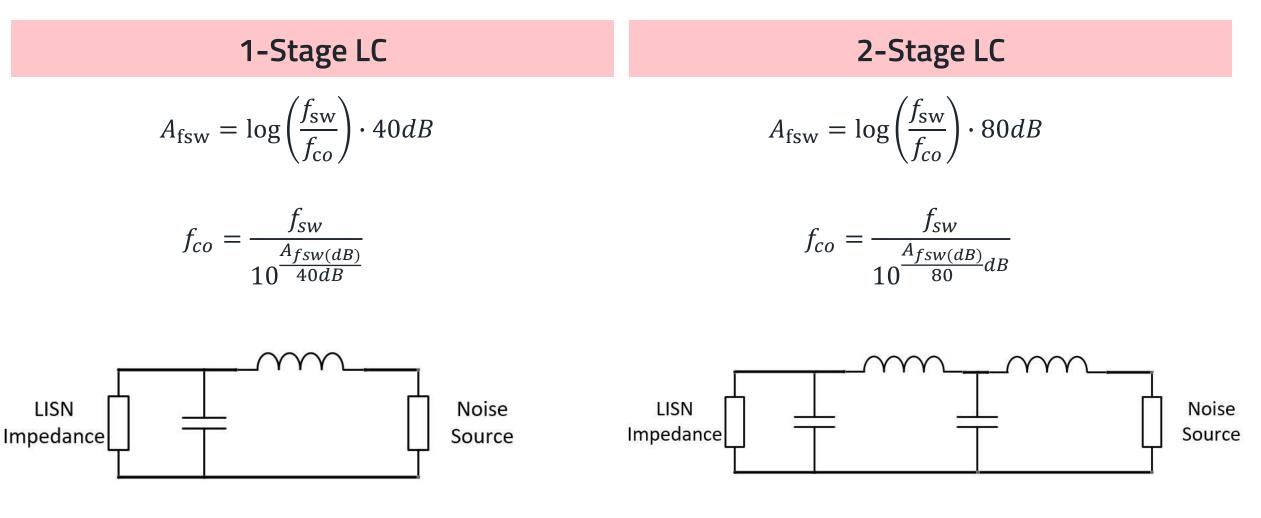

#### <u>Corner Frequency for desired Attenuation at fsw = A\_fsw</u>

Valid for both: CM & DM

#### <u>Corner Frequency for desired Attenuation at fsw = A\_fsw</u>

DM PI filter

1-Stage CLC = "PI" Additional Math for "CLC – PI"  $f_{co} = \frac{1}{2\pi \sqrt{L_{CMleak} \cdot C_{XC}}}$  $A_{\rm fsw} = \log\left(\frac{f_{\rm sw}}{f_{\rm co}}\right) \cdot 60dB$  $f_{co} = \frac{f_{sw}}{10^{\frac{A_{fsw}(dB)}{60dB}}}$  $C_{XG} = \frac{Cx1 \cdot Cx2}{Cx1 + Cx2}$ LCM\_LEAK L1 LISN Noise Impedance Source Cx1 Cx2 100Ω L2/L3

#### CLC (DM) & LC (CM) - Stage Calculation (worst case without real CM couping)

Desired damping for CM & DM = 60dB (200kHz)

- 1. "CLC PI" = 60dB/Dec (DM) and "LC" = 40dB/Dec (CM)

- 2. DM filter corner frequency: fc\_dm = 20kHz & CM filter corner frequency: fc\_cm = 6.3kHz

- **3.** Define Y-caps  $\rightarrow$  47nF(star connected)  $\rightarrow Cy_{effective} = (\frac{1}{CX1+CX2+CX3} + \frac{1}{CY})^{-1} = 47nF$

4. Define L\_cm for fc\_cm = 6.3kHz  $\rightarrow L_{cm} = \frac{1}{(2\pi fc)^2 C_y} = \frac{1}{(2\pi \cdot 6.3kHz)^2 \cdot 47nF} = 13.6mH \rightarrow 12mH$  chosen (744833120060)

5. Actual

$$f_{cm} = \frac{1}{2\pi\sqrt{L_{cm}Cy}} = \frac{1}{2\pi\sqrt{12mH\cdot47nF}} = 6.7kHz \rightarrow A_{fsw_{cm}} = \log\left(\frac{200kHz}{6.7kHz}\right) \cdot 40dB = 59dB$$

6. Calc. L\_dm

$$\rightarrow$$

XL = 54 $\Omega$ @100kHz  $\rightarrow$   $L_{dm} = \frac{XL}{2\pi f} = \frac{54\Omega}{2\pi \cdot 100 kHz} = 86 \mu H$  (use REDEXPERT for help)

7. Define

$$C_x \rightarrow C_x = \frac{1}{(2\pi f c)^2 L_{dm}} = \frac{1}{(2\pi \cdot 20 kHz)^2 \cdot 86 \mu H} = 737 nF \rightarrow 2,2 \mu$$

F chosen  $\rightarrow C_{XG} = \frac{Cx_1 \cdot Cx_2}{Cx_1 + Cx_2} = 1,18 \mu$ F (6x890334027030CS)

8. Actual

$$f_{dm} = \frac{1}{2\pi\sqrt{L_{dm}Cx}} = \frac{1}{2\pi\sqrt{86\mu H \cdot 1.18\mu F}} = 15.8 kHz \rightarrow A_{fsw_{dm}} = \log\left(\frac{200 kHz}{15.8 kHz}\right) \cdot 60 dB = 66 dB$$

# SIMULATION OF THE CALCULATED CLC FILTER

#### 4kW 3-Phase EMI Filter 150kHz - 30MHz

#### LT Spice Simulation CLC

#### LT Spice Schematic CLCLC

#### 4kW 3-Phase EMI Filter 150kHz - 30MHz

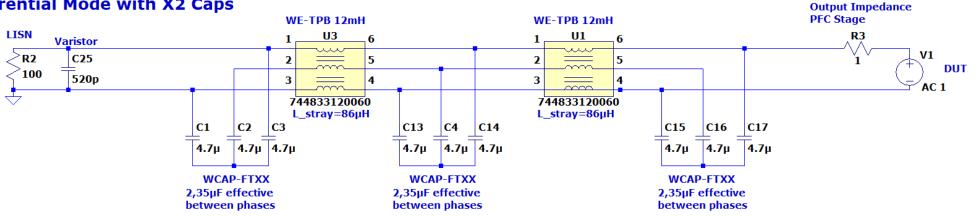

#### **Differential Mode with X2 Caps**

#### LT Spice Simulation CLCLC

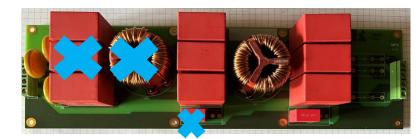

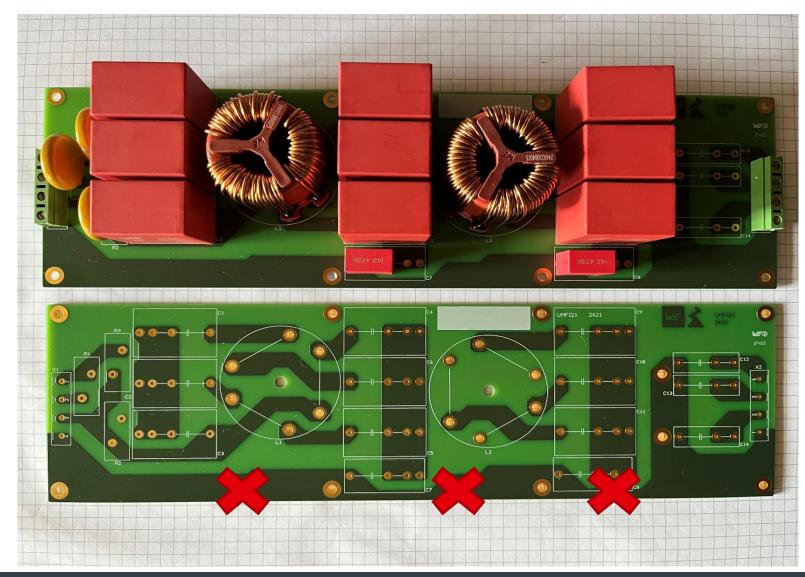

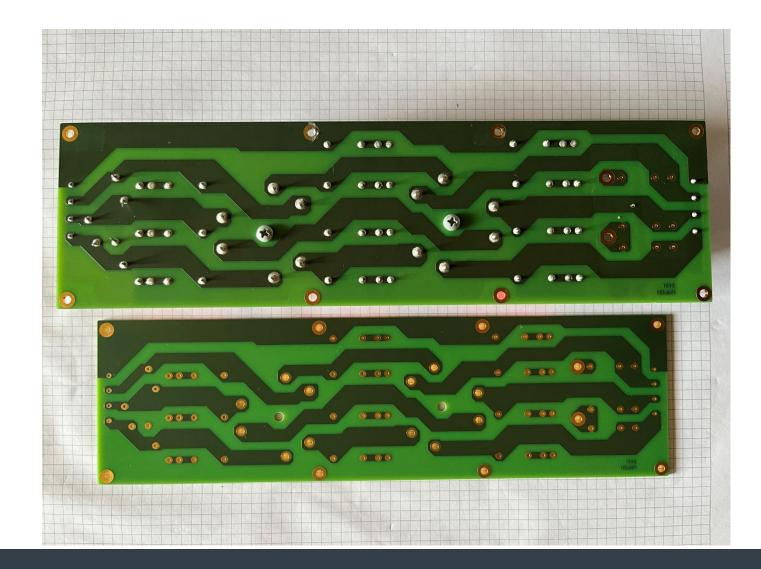

## FILTER PCB

### Example 2-Stage Design TOP view

What can be improved?

#### Example 2-Stage Design BOT view

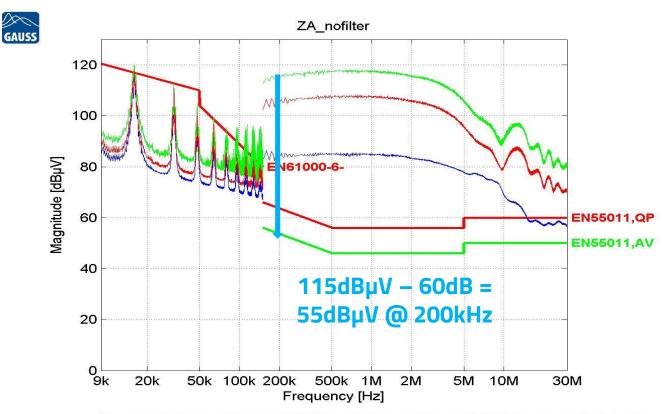

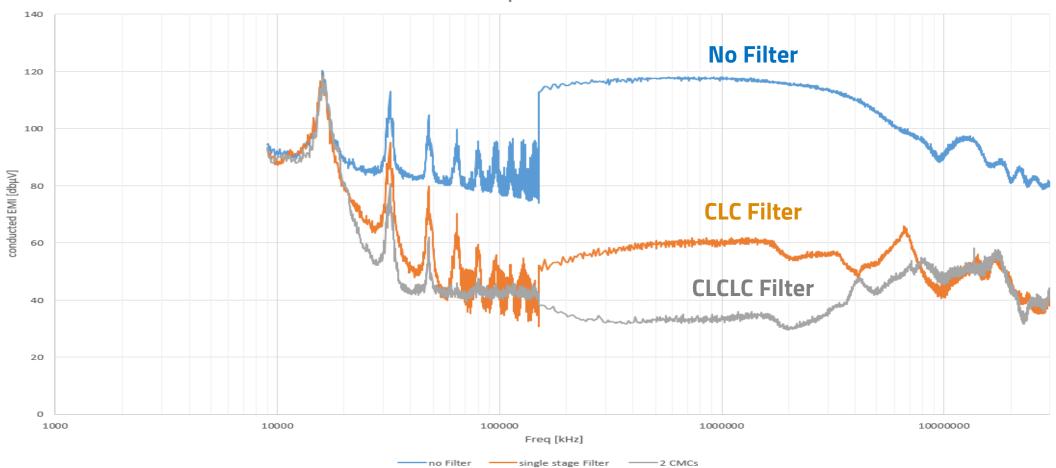

# NEW MEASUREMENTS WITH CALCULATED & SIMULATED FILTER

#### Measurements in the Lab

No Filter

Scan1: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 10.0 s, QP, TDF Standard, Att AutodB, Scan2: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 10.0 s, CAV, TDF Standard, Att AutodB, Scan3: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, MaxPeak, TDF Standard, Att AutodB, Scan4: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 10.0 s, MaxPeak, TDF Standard, Att AutodB, Scan5: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, QP, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan6: 9.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB,

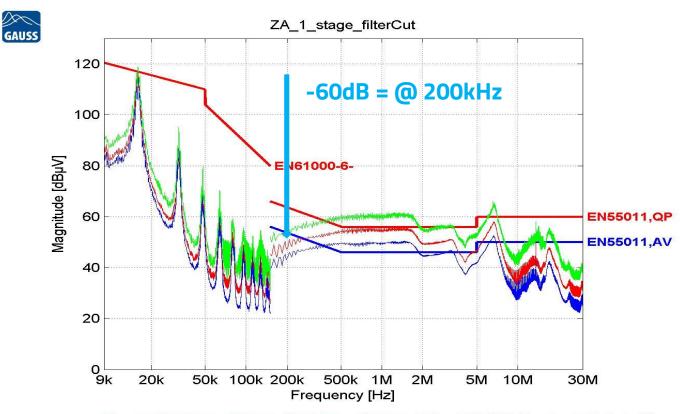

#### Measurements in the Lab

Calculated **CLC** Filter for 60dB @ 200kHz

Scan1: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 1.0 s, QP, TDF Standard, Att AutodB, Scan2: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan3: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, MaxPeak, TDF Standard, Att AutodB, \*Overf Scan4: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 1.0 s, MaxPeak, TDF Standard, Att AutodB, Scan5: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:9kHz, 1.0 s, QP, TDF Standard, Att AutodB, \*OverRange Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB, \*OverRange

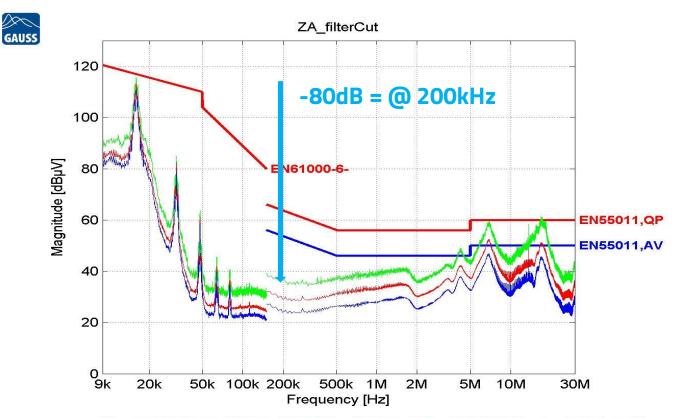

#### Measurements in the Lab

2- Stage **CLCLC** Filter for 80dB @ 200kHz

Scan1: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 1.0 s, QP, TDF Standard, Att AutodB, Scan2: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 1.0 s, CAV, TDF Standard, Att AutodB, Scan3: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, MaxPeak, TDF Standard, Att AutodB, Scan4: 150.0 kHz, 5.0 kHz, 30.0 MHz; IF:9kHz, 1.0 s, MaxPeak, TDF Standard, Att AutodB, Scan5: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:9kHz, 1.0 s, MaxPeak, TDF Standard, Att AutodB, Scan5: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, QP, TDF Standard, Att AutodB, Scan6: 9.0 kHz, 100.0 Hz, 150.0 kHz; IF:200Hz, 1.0 s, CAV, TDF Standard, Att AutodB,

#### **Overview**

3 phase Filter

#### **Deviation between Math, Simulation and Real Test**

Why don't we get so much attenuation as simulated?

- CMC tolerance

- Cap tolerance

- Coupling between components

- Layout coupling (e.g. PE/chassis connection in multi stage filter)

- Grounding impedance is to high

- Wrong system impedance estimation

- Wrong DM CM separation setup

- CMC saturation (e.g. applications with high dv/dt and long unshielded motor cables)

- Nominal CMC inductance does not match with impedance curve at requiered frequency

## **Y-CAP LEAKAGE**

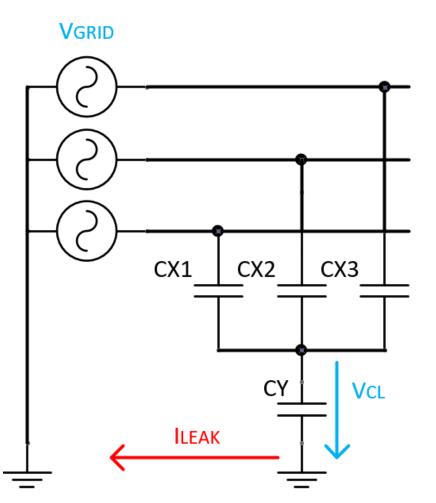

#### Y-Cap leakage

3-phase system with X-cap star connection

- In a balanced capacitor networtk, the sum of all 3 line currents are zero

- In theory, if all X-caps are equal, there will be no leakage

- In reality, the tolerances of the X-caps will cause some leakage

- The highest leakage occur at the highest unbalance between the phases

- Cause for the unbalance are the tolerances of the grid voltage & caps

- Assume 3% tolerances for grid voltage and 10% for caps

$$I_{leak,max} = V_{CL} \cdot 2\pi f \cdot C_{Y,max}$$

$$|I_{leak,max}| = 2\pi f \cdot C_{Y,max} \cdot \frac{V_{GRID,max} \cdot C_{X,max} - V_{GRID,min} \cdot C_{X,min}}{C_{X,max} + 2 \cdot C_{X,min} + C_{Y,max}}$$

#### Y-Cap leakage

3-phase system with X-cap star connection

- Example calculation

- Cx = 2.2µF / Cy = 100nF / +10% tolerance

- 400VAC grid 50Hz +-3% tolerance (EN50160)

$$|I_{leak,max}| = 2\pi f \cdot C_{Y,max} \cdot \frac{V_{GRID,max} \cdot C_{X,max} - V_{GRID,min} \cdot C_{X,min}}{C_{X,max} + 2 \cdot C_{X,min} + C_{Y,max}}$$

$$\left|I_{leak,max}\right| = 2\pi 50 Hz \cdot 110 nF \cdot \frac{412V \cdot 2.42\mu F - 388V \cdot 1.98\mu F}{2.42\mu F + 2 \cdot 1.98\mu F + 110nF} = 1.22 mA$$

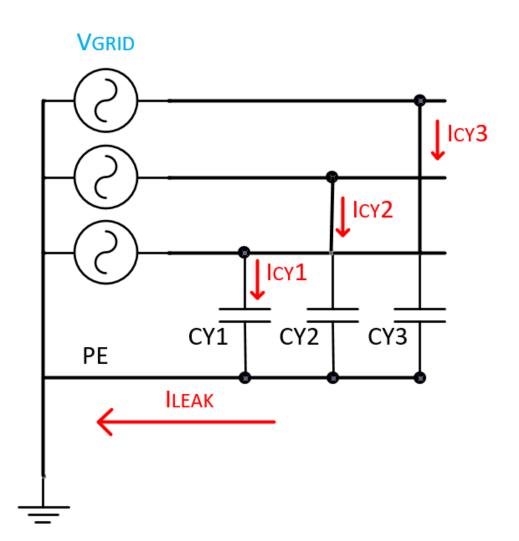

#### Y-Cap Leakage

3-phase system

- In a perfect symmetrical / balanced system there is no leakage

- In reality a 3-phase filter is always loaded unbalanced:

- →Y-cap tolerances

- $\rightarrow$  Imbalance of the supply grid

- → Asymmetrical load

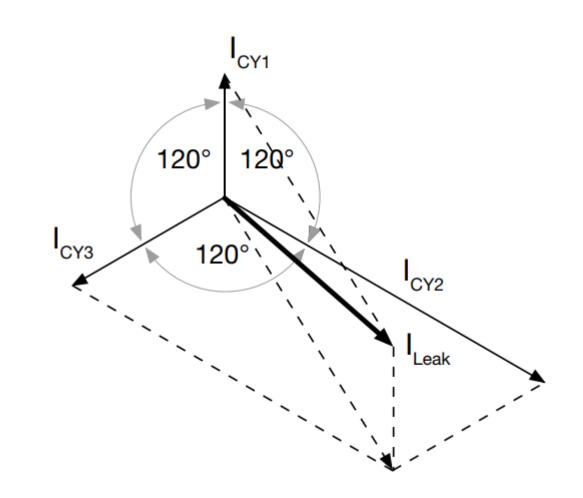

#### Y-Cap leakage

3-phase system

- The leakage currents of the vecotors of the phases need to be added together to determine the resulting discharge current!

- Practical assumption: Cy: 100nF / 50Hz / 400V

$|I_{leak,max}| = 2\pi f \cdot (C_{Y,max} - C_{Y,min}) \cdot V_{Grid}$

$|I_{leak,max}| = 2\pi 50 Hz \cdot (110 nF - 90 nF) \cdot 400 V = 2.51 mA$

## **DISCHARGE RESISTOR**

#### **Caps Discharge Resistor**

Voltage after power plug removed: In 1 second

• Power rating resistor:

$$Pv = \frac{V_{Line}^2}{R_{Discharge}}$$

- e.g.  $R = 220k\Omega \rightarrow 720mW@400V$

- Total capacitance:  $C_{tot} = C_{X1} + C_{X2} + C_{ParaMOV} + (\frac{1}{\frac{1}{C_{Y1}} + \frac{1}{C_{Y2}}})$

- Cap discharge voltage decay:  $V = V_{Grid} \cdot e^{-(t/RC)}$

- Example:

•

$$C_{tot} = 2,2\mu F V_{Grid} = 400V R = 220k\Omega t = 1sec$$

•  $V = V_{Grid} \cdot e^{-\left(\frac{t}{RC}\right)} = 400V \cdot e^{-1s \div (220k\Omega \cdot 2,2\mu F)} = 50,6V$

- <u>Capacitor Safety Discharge Conversion Calculator | DigiKey</u>

- Take care of: creepage, clerance and voltage rating when choosing the discharge resistor!

# VARISTOR FOR 4KV SURGE TEST

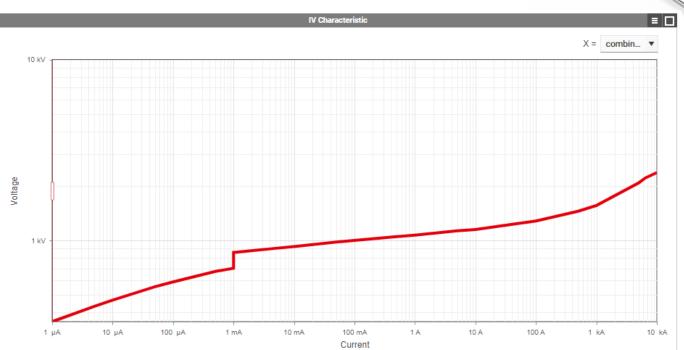

#### <u>Varistor</u>

Typical 3-Phase , 4kV Surge Test

- Industrial inverter with 400 V AC voltage supply

- Surge test according to DIN EN 55024

- Coupling type: symmetrical (phase to neutral conductor)

- Test voltage: U<sup>^</sup>\_G= 4kV

- Coupling impedance (= internal resistance of the test generator):

- $Z_{\rm G} = 2\Omega$

- Selection of the varistor:

- Operating voltage taking into account the tolerance:

- *U*\_rms = 460*V*

- 20 mm high surge disk varistor WE-VD 820424611

- Specification:

- Voltage at the electronics should not exceed 1.6kV

#### **Electrical Properties:**

| Properties                   |                    | Test conditions | Value | Unit | Tol. |

|------------------------------|--------------------|-----------------|-------|------|------|

| AC Operating Voltage         | V <sub>RMS</sub>   |                 | 460   | V    | max. |

| DC Operating Voltage         | V <sub>DC</sub>    |                 | 615   | V    | max. |

| Clamping Voltage             | V <sub>Clamp</sub> | 100 A @ 8/20 µs | 1240  | V    | max. |

| (Reverse) Peak Pulse Current | I <sub>Peak</sub>  | 8/20 µs         | 10000 | Α    | max. |

| Power Dissipation            | P <sub>Diss</sub>  |                 | 1     | W    | max. |

| Energy Absorption            | W <sub>max</sub>   | 10/1000 µs      | 440   | J    | max. |

| Nominal Discharge Current    | ۱ <sub>n</sub>     |                 | 5     | kA   | max. |

| Measured Limiting Voltage    | V <sub>ML</sub>    |                 | 1690  | V    | max. |

| (Reverse) Breakdown Voltage  | V <sub>BR</sub>    | 1 mA            | 750   | V    | ±10% |

| (Channel) Input Capacitance  | C <sub>Ch</sub>    | 1 kHz           | 520   | рF   | typ. |

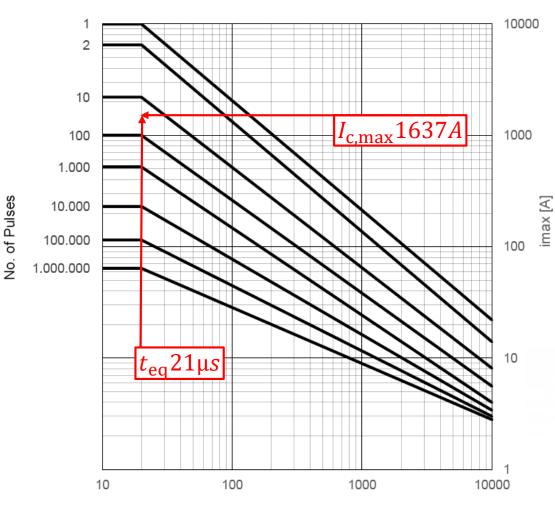

#### Varistor 3-Phase / 4kV Surge

Determination of operating point Alternative iterative calculation (use Redexpert V/I max. curve for reading)

• Step 1: Determination of the maximum clamping voltage for the short-circuit current of the test generator ( $\hat{V}_G$ =4kV/ $Z_G$ = 2 $\Omega$  / 2kA / 400V x 1.41)  $\rightarrow I_G = \frac{V_G + V_{Grid}}{Z_G} = \frac{4kV + 564V}{2\Omega} = 2282A$

V/I characteristic curve +10% tolerance:  $V_{CALMP_{max}@2282A} \rightarrow 1.69kV$

- Step 2: Calculation of the new current value through the variator using the known coupling impedance  $Z_{\rm G}$  and V\_clamp\_max:  $I_{\rm C1} = \frac{V_{\rm G} + V_{\rm Grid} V_{\rm CLAMP_{max}}}{Z_{\rm G}} = \frac{4kV + 564V 1.69kV}{2\Omega} = 1437A$

- V/I characteristic curve +10% tol. :  $V_{CALMP@1437A} \rightarrow 1.56 kV \checkmark$

- Step 3: Determine max. I\_clamp through varistor using the V/I curve with -10%

- $V_{CALMP_{min}@1437A} \rightarrow 1.29kV$

- Step 4: Calculate the max. current through the variator:  $I_{C_max} = \frac{V_G + V_{Grid} V_{CLAMP_{min}}}{Z_G} = \frac{4kV + 564V 1.29kV}{2\Omega} = 1637A$

#### **Varistor**

Typical 3-Phase, 4kV Surge Test

- Check how many 8/20µs current pulses the varistor can withstand

- Determining the equivalent width of the square-wave current pulse

$t_{eq,8/20} = 0.5 \cdot T_1 + 1.43 \cdot (T_2 - T_1)$ = 0.5 \cdot 8\mus s + 1.43 \cdot 12\mus = 21.16\mus

- The varistor can withstand approx. 50 @ 21µs pulses with 766A

- What is the maximum energy occurring in the varistor during the test? → 40 pulses ✓

#### **Pulse Lifetime Derating:**

Pulse Duration [µs]

#### **Varistor**

Typical 3-Phase, 4kV Surge Test

• Maximum energy occurring in the varistor:

$W_{\rm V} = I_{\rm clamp,max} \cdot U_{\rm clamp,min} \cdot t_{\rm eq,8/20} = 1637 \text{A} \cdot 1290 \text{V} \cdot 21,16 \mu \text{s} = 44.7 \text{Ws}$

- Datasheet:  $W_{\rm max} = 440 {

m Ws}$  (Joule) 🗸

- The maximum power loss is specified as P\_max=600mW. The minimum necessary recovery time (cooling of the component) is therefore given as:

$$T > \frac{W_{\rm V}}{P_{\rm max}} = \frac{44.7 \,{\rm Ws}}{1 \,{\rm W}} = 44.7 \,{\rm s}$$

The basic standard DIN EN 61000-4-5 requires a maximum recovery time of 60 seconds. The varistor fulfills this criterion.