# **BASIC DESIGN RULES**

LAYOUT ACCORDING TO THE WE PARAMETERS AND THE PCB FITS

Andreas Schilpp

**WURTH ELEKTRONIK** MORE THAN YOU EXPECT

# **WELCOME TO THE ANNIVERSARY WEBINAR**

#### 10 Years of Würth Elektronik PCB Webinars

The first webinar of your Top 3, originally offered in May 2013, is more current than ever: Recently, the Würth Elektronik BASIC Design Rules have been updated and restructured.

First webinar: 7 May 2013

■ EN: 47 Attendees

# **AGENDA**

BASIC Design Rules: Layout according to the WE parameters and the PCB fits

- 1. BASIC and standard what is the difference?

- 2. Introduction of the new BASIC Design Rules

- Scope of application

- Contents

- What is different?

- 3. Background information on the changes

- Processes for copper structuring

- Specification of copper thickness according to IPC

- Aspect ratio for holes

- 4. Application of the BASIC Design Rules an example

**Andreas Schilpp**Technical Marketing

# **BASIC AND STANDARD – WHAT IS THE DIFFERENCE?**

#### **Definitions**

#### **STANDARD**

- a <u>category</u> or <u>classification</u>

- available from all plants

- at a favorable standard price

- other categories are

- Advanced

- (Leading Edge / State-of-the-Art)

- Standard / Advanced are available in all technologies

#### Further example for standards

- Standard Stackup

- Material in stock, processes standardized

- Standard processes ensure high quality and favorable prices with short delivery times

#### **BASIC**

- a <u>technology</u>. By <u>BASIC</u> technology we mean

- single-sided,

- double-sided and

- multilayer printed circuit boards.

# <u>TIP</u> USE STANDARDS

#### Use of standards:

- Standard material

- Material database of the PCB manufacturer (if available)

- Standard layer stackups also digital for import

- Standard design rules

- Standard delivery specification

- Standard packaging

<u>.</u> .

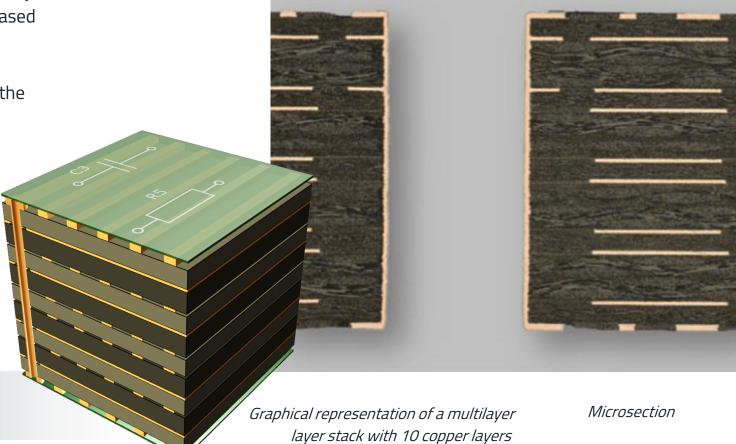

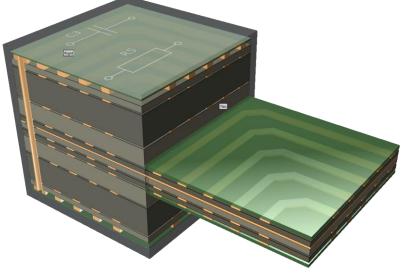

# **BASIC TECHNOLOGY – VARIANT MULTILAYER**

The third generation in the history of PCBs is characterised by a multilayer structure, created by pressing copper foil, FR4 based copper-clad inner layer cores and pre-pregs.

The obvious additional effort and higher costs are offset by the many advantages:

More layers to route complex components, such as BGA packages

Possibility to design power supply systems to improve power integrity and EMC.

Possibility to design transmission lines with defined impedance to improve signal integrity

Multilayer PCBs make use of small through hole vias, also known as PTH (plated through holes), to connect layers

#### Contents

| 1  | Scope of application                          | O: |

|----|-----------------------------------------------|----|

| 2  | Basic notes                                   | 0  |

| 3  | BASIC base material                           | 0  |

| 4  | BASIC Standard Stackups                       | O  |

| 5  | Copper structures, spacings                   | 04 |

| 6  | Drills, drill pads, annular rings, clearances | 06 |

| 7  | Edge plating                                  | 07 |

| 8  | Solder mask                                   | 07 |

| 9  | Peelable masking                              | Œ  |

| 10 | Markings                                      |    |

#### Scope of application

- The BASIC design parameters (copper structures or spacing, holes, solder mask, markings and solder surfaces) are basically valid for all PCB technologies, beyond BASIC for example also for

- HDI Microvia,

- Embedding technology or

- Flex solutions.

#### Flyer

### Flyer

## Flyer

# 8 SOLDER MASK

Laquer residues in via holes

Follow-up error ENIG Surface

# BASIC DESIGN RULES: LAYOUT ACCORDING TO THE WE PARAMETERS

Poll: Multiple choice with only one correct answer

What has the greatest influence on the minimum copper spacing (subtractive etching technique on inner layers)?

- Number of layers

- Thickness of the copper foil

- Thickness of the electroplated metallization

- Total thickness of copper foil and electroplated metallization

- Prepreg thickness

Flyer: What is new?

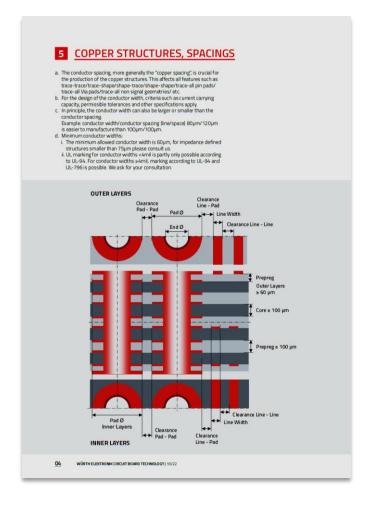

- a. The conductor spacing, more generally the "copper spacing", is crucial for the production of the copper structures. This affects all features such as tracetrace / trace-shape / shape-trace / shape-shape / trace-all pin pads / trace-all Via pads / trace-all non signal geometries / etc..

- b. For the design of the conductor width, criteria such as current carrying capacity, permissible tolerances and other specifications apply.

- c. In principle, the conductor width can also be larger or smaller than the conductor spacing.

- Example: conductor width/conductor spacing (line/space) 80  $\mu m$  / 120  $\mu m$  is easier to manufacture than 100  $\mu m$  / 100  $\mu m$ .

- d. Minimum conductor widths:

- i. The minimum allowed conductor width is 60 μm, for impedance defined structures smaller than 75 μm please consult us.

- II. UL marking for conductor widths <4 mil is partly only possible according to UL-94. For conductor widths ≥ 4mil, marking according to UL-94 and UL-796 is possible. We ask for your consultation.

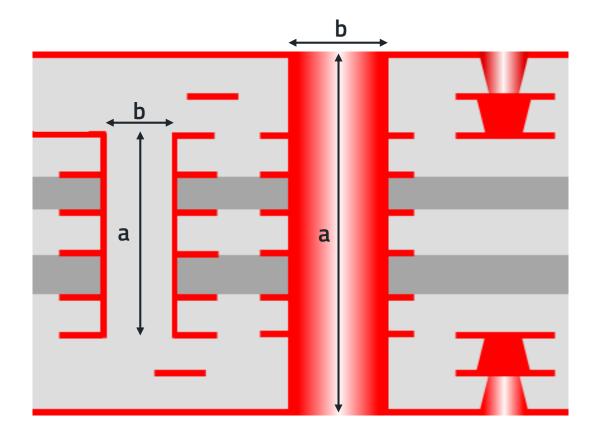

# 5 COPPER STRUCTURES, SPACINGS

Feature to Feature Spacing

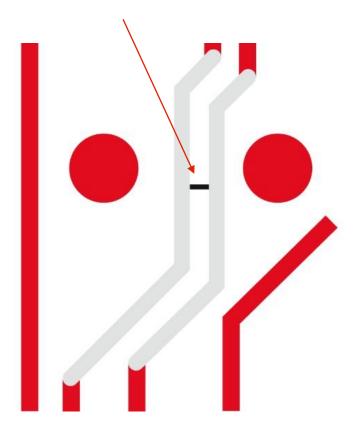

# **BASICS: COPPER STRUCTURING**

Inner layers: Imaging positive + etching subtractive

CUSTOMER DATA

**RESIST**

**BASE COPPER**

**BASE MATERIAL**

Flyer: What is new?

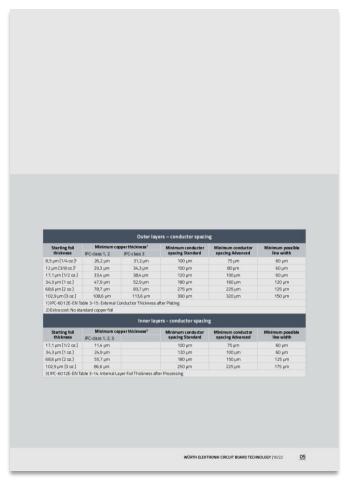

5 COPPER STRUCTURES, SPACINGS

Table for inner layers

| Inner layers - conductor spacing                                           |                                       |  |                   |                   |                  |  |

|----------------------------------------------------------------------------|---------------------------------------|--|-------------------|-------------------|------------------|--|

| Starting foil                                                              | Minimum copper thickness <sup>3</sup> |  | Minimum conductor | Minimum conductor | Minimum possible |  |

| thickness                                                                  | IPC-class 1, 2, 3                     |  | spacing Standard  | spacing Advanced  | line width       |  |

| 17,1 μm [1/2 oz.]                                                          | 11,4 µm                               |  | 100 μm            | 75 µm             | 60 µm            |  |

| 34,3 µm [1 oz.]                                                            | 24,9 µm                               |  | 120 µm            | 100 µm            | 60 µm            |  |

| 68,6 µm [2 oz.]                                                            | 55,7 μm                               |  | 180 µm            | 150 µm            | 125 µm           |  |

| 102,9 μm [3 oz.]                                                           | 86,6 µm                               |  | 250 µm            | 225 μm            | 175 µm           |  |

| 3) IPC-6012E-EN Table 3-14: Internal Layer Foil Thickness after Processing |                                       |  |                   |                   |                  |  |

# **BASICS: COPPER STRUCTURING**

Outer layers: Imaging negative + copper deposition selective + etching base copper

**CUSTOMER DATA**

**TIN RESIST**

**PHOTORESIST**

**COPPER PLATING**

**BASE COPPER**

**BASE MATERIAL**

Flyer: What is new?

Table for outer layers

| Outer layers – conductor spacing                                        |                                       |             |                   |                   |                  |  |

|-------------------------------------------------------------------------|---------------------------------------|-------------|-------------------|-------------------|------------------|--|

| Starting foil                                                           | Minimum copper thickness <sup>1</sup> |             | Minimum conductor | Minimum conductor | Minimum possible |  |

| thickness                                                               | IPC-class 1, 2                        | IPC-class 3 | spacing Standard  | spacing Advanced  | line width       |  |

| 8,5 µm [1/4 oz.] <sup>2</sup>                                           | 26,2 μm                               | 31,2 µm     | 100 µm            | 75 µm             | 60 µm            |  |

| 12 μm [3/8 oz.] <sup>2</sup>                                            | 29,3 μm                               | 34,3 µm     | 100 µm            | 80 µm             | 60 µm            |  |

| 17,1 µm [1/2 oz.]                                                       | 33,4 µm                               | 38,4 µm     | 120 µm            | 100 μm            | 60 µm            |  |

| 34,3 µm [1 oz.]                                                         | 47,9 μm                               | 52,9 μm     | 180 µm            | 160 µm            | 120 µm           |  |

| 68,6 µm [2 oz.]                                                         | 78,7 μm                               | 83,7 μm     | 275 μm            | 225 μm            | 125 μm           |  |

| 102,9 μm [3 oz.]                                                        | 108,6 μm                              | 113,6 μm    | 390 µm            | 320 µm            | 150 µm           |  |

| 1) IPC-6012E-EN Table 3-15: External Conductior Thickness after Plating |                                       |             |                   |                   |                  |  |

| 2) Extra cost: No standard copper foil                                  |                                       |             |                   |                   |                  |  |

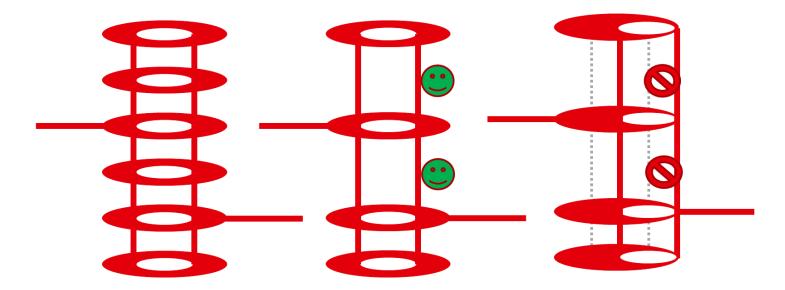

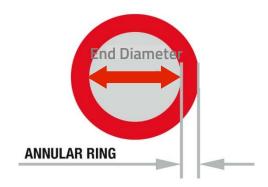

Why are annular rings needed around via holes?

- Relationship between via pad size, registration and drill diameter

- Annular ring specifications of IPC classes (see IPC-2221)

- Influence of the drill tool: deflection

- Influence of the machine

- Layout-dependent shrinkage/expansion values: Offset of layers relative to each other

- Ideal versus real

Important for the drill diameter: Aspect ratio - next slide

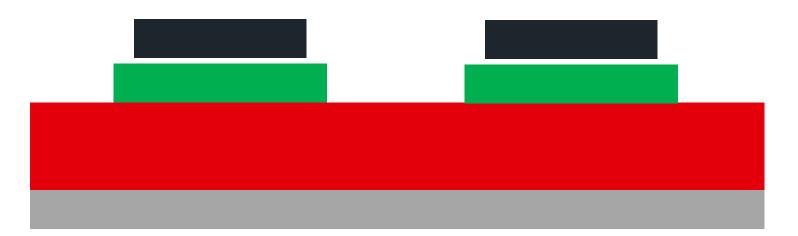

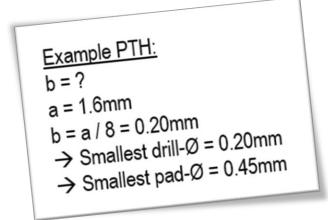

#### **Aspect Ratio**

- Ratio drill-diameter b drill depth a

- PTH & BV: max. 1:8

- Important for a complete and even copper build-up in the barrel.

# DRILLS, DRILL PADS, ANNULAR RINGS, CLEARANCES

#### Table

| Plated Through Holes                                                                               |                                                               |                           |                        |                           |                         |                                                            |

|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|------------------------|---------------------------|-------------------------|------------------------------------------------------------|

| Pad size                                                                                           | Remark                                                        | Aspect Ratio <sup>1</sup> | Drill tool<br>diameter | Finished<br>hole diameter | Tolerance<br>(Standard) | Copper clearance<br>plane on<br>inner layer<br>without Pad |

| 0,60 mm                                                                                            | Standard  Max. ca. 12 layers  Max. ca. 1,80 mm  PCB thickness | 8:1                       | 0,35 mm                | 0,25 mm                   | +0,1/-0,05 mm           | ≥ 0,80 mm                                                  |

| 0,55 mm                                                                                            |                                                               |                           | 0,30 mm                | 0,20 mm                   |                         | ≥ 0,75 mm                                                  |

| <b>0,50 mm</b><br>(Cu max. 35 μm)                                                                  |                                                               |                           | 0,25 mm                | 0,15 mm                   |                         | ≥ 0,70 mm                                                  |

| <b>0,45 mm</b><br>(Cu max. 35 μm)                                                                  | For less complex<br>Layer stackups                            |                           | 0,25 mm<br>(0,20 mm)   | 0,15 mm                   |                         | ≥ 0,70 mm                                                  |

| 1) Aspect Ratio" for drill holes: Ratio of drill hole length or depth to drill hole tool diameter. |                                                               |                           |                        |                           |                         |                                                            |

<sup>1)</sup> Aspect Ratio" for drill holes: Ratio of drill hole length or depth to drill hole tool diameter. For further information, see technical delivery specification chapter 3.7.1.

Why do you need copper releases in ground inner layers without a pad?

vily do you need copper releases in ground inner layers without a pad

Non-used / non-functional pads:

- Pad removal does not add space on inner layers because tolerances, offset and deflection are real and permissible.

- A design rule check must be performed before pad removal!

- The total clearance is pad size plus minimum copper clearance!

Annular ring

ATTENTION with RIGID.flex:

<u>Do NOT remove</u> non-used /

non-functional via pads on flex layers for reliability reasons!

# **BASIC DESIGN RULES: LAYOUT ACCORDING TO THE WE PARAMETERS**

Usage of table for UFBGA 7X7X0.6 169L P 0.5mm

**TOP** Layer 2 Layer 3 Layer 4

## BASIC DESIGN RULES: LAYOUT ACCORDING TO THE WE PARAMETERS

Poll: Multiple choice with only one correct answer

Please rate the BASIC Design Rules: How many points on a scale of 1 to 10 do you give the document?

- 1 to 2 points (unusable)

- 3 to 4 points (incomplete and incorrect)

- 5 to 6 points (ok, but incomplete)

- 7 to 8 points (good, helpful, understandable)

- 9 to 10 points (almost perfect, I use it often)

#### **NOTES**

- → Participants with a rating of less than 5 points I will contact in writing after the webinar (this is not a threat, but a partnership offer!)

- → Feel free to write me errors, additions and optimizations in the question field

## **SUMMARY**

#### New BASIC Design Rules

- BASIC is a technology

- Standard is a category or classification

- Conductor spacing is important for PCB manufacture

- Conductor width and conductor spacing should be considered independently of each other. Different values should be considered at least locally.

- Annular rings around via holes are still necessary

- Non-used pad removal does not save space

- Würth Elektronik Webinars more than you expect!