# HDI MICROVIA

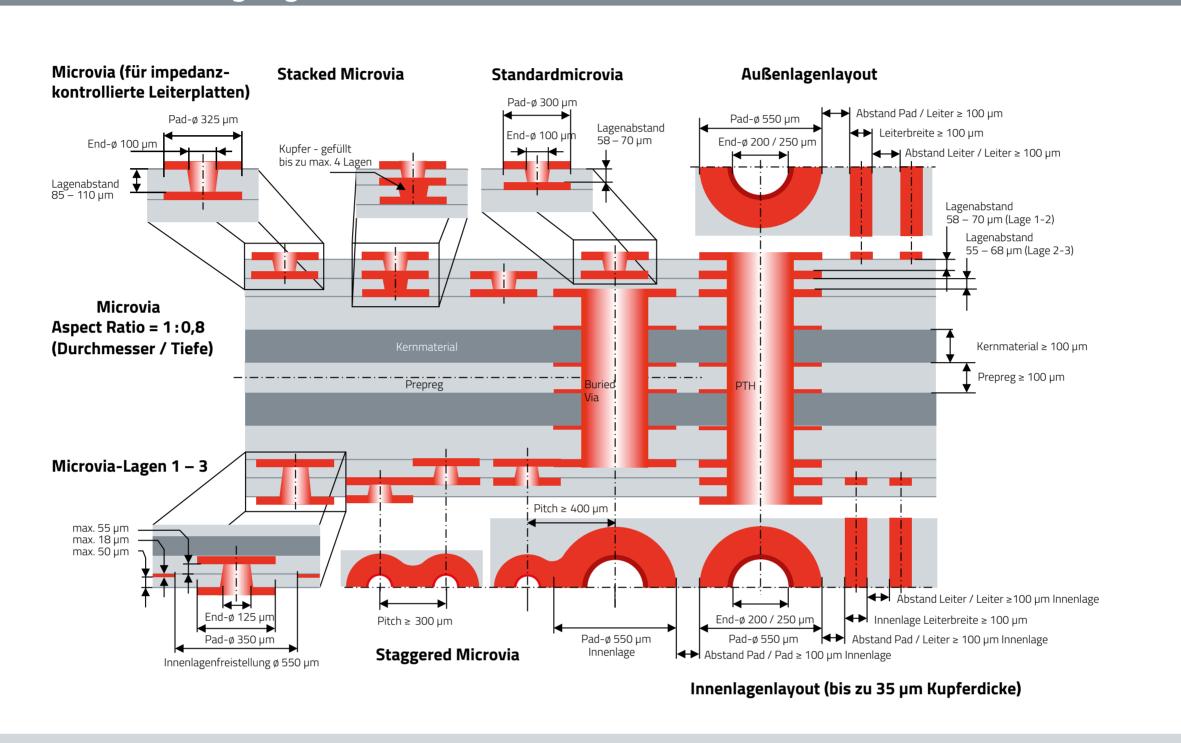

#### **HDI Microvia Standard Designregeln**

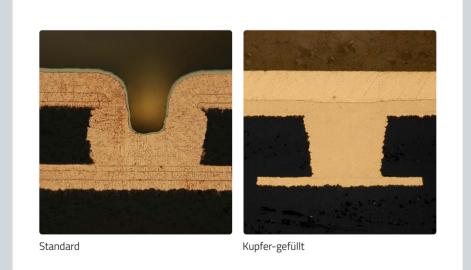

#### Microvia Standard und Kupfer-gefüllt

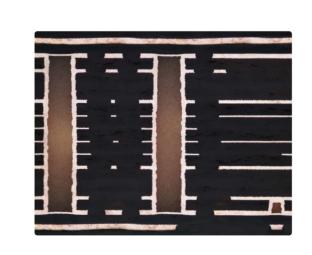

#### Filled & Capped Via und Microvia

### PTH und Via filled & capped (IPC-4761, Type VII)

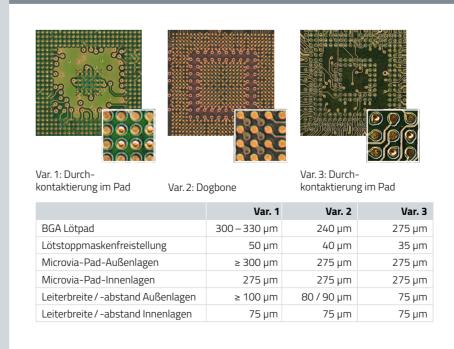

#### BGA 0,80 mm Pitch

durchgehenden Vias

Microvias

|                                    | Var. 1      | Var. 2       | Var. 3       |

|------------------------------------|-------------|--------------|--------------|

| BGA Lötpad                         | max. 400 µm | _            | max. 500 μm  |

| Lötstoppmaskenfreistellung         | 50 µm       | ≥ 50 µm      | 50 µm        |

| Via Padgröße BGA Bereich           | 500 µm      | _            | _            |

| Microvia-Pad-Außenlagen            | _           | 300 / 350 µm | 300 / 350 μm |

| Microvia-Pad-Innenlagen            | _           | 300 / 350 µm | 300 / 350 μm |

| Leiterbreite / -abstand Außenlagen | ≥ 100 µm    | ≥ 100 µm     | ≥ 100 µm     |

| Leiterbreite / -abstand Innenlagen | ≥ 100 µm    | ≥ 100 µm     | ≥ 100 µm     |

BGA 0,50 mm Pitch

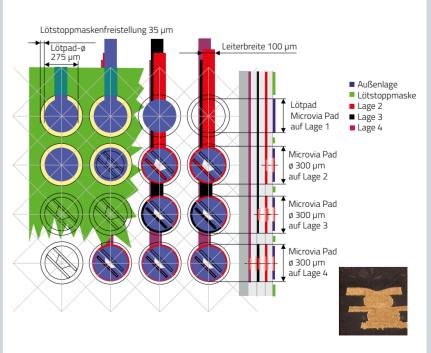

## BGA 0,40 mm Pitch Lötstoppmaskenfreistellung 35 µm

**MORE SUPPORT THAN YOU EXPECT**  Welche Basismaterial Qualitäten in einer Leiterplatte verwendet werden, ist aus dem Lagenaufbau erkennbar. Würth Elektronik bietet kosten- und fertigungstechnisch optimierte Standard Stackups auf der Webseite an. Hier finden Sie auch alle Standards als digitale Stackup Dateien zum Import in Ihre EDA Software.

Sie haben Fragen zu Fertigungsdaten, Toleranzen, Prüfdokumentation oder Verpackung? In unserer Technischen Lieferspezifikation für Leiterplatten (TLS) finden Sie unsere Standards und Empfehlungen für eine reibungslose und effektive Zusammenarbeit.