## **DESIGN KIT** WE-XTAL Through Hole and Surface Mount Metal Can Quartz Crystals

- Introduction

- Specification requirements

- Time Keeping with Quartz Crystals

- Quartz Crystal Handling Precautions

Version 1.0 Order Code 830 003

### Introduction

## **Specification requirements**

Quartz Crystals are used across the electronics industry to produce an accurate and stable frequency reference. Applications are many, varied and include microprocessor timing, phase lock loops, analogue to digital sampling, communication timing etc.

Before quartz crystals, timing was derived from the decay of a capacitive change limited through a resistor, this gave accuracy and stability of a few percent, or tens of thousands of Parts Per Million (ppm). Due to the high Q factor quartz crystals give greatly improved accuracy and stability down to a few ppm.

Quartz crystal have a peizo electric effect, meaning there is a coupling between electrical and physical motion. An effect first discovered by Pierre Curie and Jacques Curie. The first practical application of this effect came with the invention of Sonar in 1917. Quartz timing devices became significant in the 1940s to control the carrier wave of the radio transmission on aeroplanes, where the rapid changes of temperature, pressure and humidity caused great problems for RC based circuits.

By designing the quartz crystal to have one specific resonant frequency, then placing this crystal in the feed back loop of an oscillator, a simple oscillation circuit can be made that will electrically resonate at a frequency dictated by the quartz shape. Break down of specification required to be able to quote the correct part:

- 1 Frequency of oscillation: (MHz)

- 2 Model Name or Package size: (mm)

- 3 Tolerance: (±ppm). The maximum acceptable deviation from the required frequency of oscillation, when at 25 °C

- 4 Stability: (±ppm), The maximum frequency deviation across the temperature range, referenced to the frequency at 25 °C (Tolerance)

- 5 Temperature Range: (°C). The temperature range over which the stability will be within specification

- 6 Load Capacitance: (pF). The combined capacitance presented to the crystal by the PCB. Including any stray capacitance

- 7 Overtone Order: The number of physical oscillations within the quartz. In most cases this will be fundamental

## **Timekeeping with Quartz Crystals**

This application note is intended to give some guidance as to the use of quartz crystals in time keeping applications.

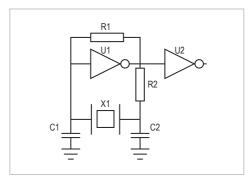

The standard circuit used to achieve oscillation of a crystal is the Pierce oscillator circuit (see Figure 1). Here the crystal is placed in the feed back loop of an inverting amplifier (U1), which can be a simple inverting buffer with a resistor (R1) between the input and output to force the buffer to become a high gain amplifier. At resonance the crystals capacitive and inductive impedance cancel out and leave only the resistive impedance, this occurs at 180 °C phase, it is for this reason that an inverting amplifier is necessary to achieve a 360 °C phase shift in the feed back loop.

A further resistor (R2) is necessary to limit the current through the feed back loop. The circuit is very sensitive therefor needs to be buffered (U2) from any external influence.

The capacitors (C1 and C2) plus the stray capacitance of the PCB plus the stray capacitance of the input and output pins of the buffers must be added together, this combined value gives the capacitance element which is seen by the crystal, this is called Capacitive Load, CL, and must equal the CL of the crystal data sheet. The correct way to add these values is as follows:

$$\frac{C1 \times C2}{C1 + C2} + CStray = CL$$

Any discrepancy in CL will cause a frequency offset. Therefore it is important that the values C1 and C2 are constant. For this reason it is recommended to use NPO COG or similar low temperature coefficient capacitors.

Figure 1

The circuit given in Figure 1 can be made using a standard 4060 IC in which the crystal is connected across pins 10 and 11 and the frequency can be seen at pin 9. Values for components will vary depending on the specific crystal used, but the following values have been found to be a good starting place for further experimentation. R1:  $1 \text{ M}\Omega$ , R2:  $1 \text{ k}\Omega$ . Stray capacitance on the IC can vary significantly dependent on

manufacturer and PCB stray is down to the design. A starting figure of 6 pF for total stray capacitance is not unreasonable. Therefore, for a crystal with a known CL of 16 pF values for C1 and C2 should be around 20 pF each.

The most common application for quartz crystals is as the clock of a microprocessor. In this application U1 and U2 are internal to the microprocessor. It is also common that R1 and R2 are also within the microprocessor.

## **Timekeeping with Quartz Crystals**

If the CL seen by the crystal matches that on the crystal data sheet then the circuit will resonate at the required frequency within the Tolerance given on the data sheet.

For best results the follow PCB design considerations should be observed:

- The crystal should be mounted as close as possible to the IC to reduce the track length and thus reduce both stray capacitance and reflection waves.

- Avoid Ground Loops as variations in ground will be translated directly into drive level changes and thus frequencies changes.

- Keep Digital and power traces as far away from the crystal traces as possible to avoid cross talk.

- Where applicable connect the crystal housing to ground to reduce EMI noise.

- Guard the crystal traces with ground traces (guard ring).

Use a clean ground with no current to or from other devices flowing through the guard ring. Connect the guard ring to the microprocessor ground.

- Most microprocessors include a ground connection on a pin directly next to the crystal pins, this will be an internally isolated ground and should be used only for the crystal circuit.

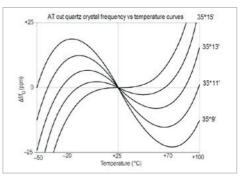

The frequency of a crystal based oscillator circuit will show a repeatable change with a change in ambient temperature. Crystals in the MHz range have been cut from the original crystal bar at an angle of  $35^{\circ}15'$ , this cut is known in the industry as the AT cut and it gives a frequency vs temperature change in the form of a cubic response (Figure 2).

Figure 2

At the design stage, the cut angle is varied by a few seconds of a degree to optimise the frequency vs temperature behaviour of the crystal and best meet the specific requirements of the data sheet.

## **Crystal Handling Precautions**

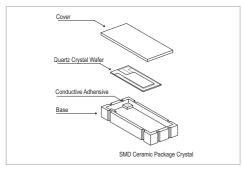

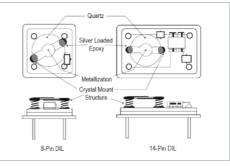

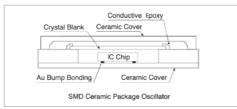

#### **Crystal Unit Structure**

A quartz crystal unit includes a small strip or disk of quartz that is processed to an exact size and thickness dependent on the customer specified resonating frequency. The quartz is plated with conducting electrodes and mounted in a hermetically sealed protective enclosure (see Figure 1).

The electrodes connect to leads that pass through the base assembly via glass-to-metal seals or, in the case of a SMD ceramic package (see Figure 1); the electrodes connect to the pads via layered plated ceramic.

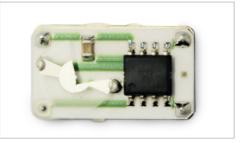

Crystal units are often encapsulated together with other circuitry to realize a fully functional module, e.g. an oscillator or a complex filter. Figure 3 illustrates simple crystal oscillators. Because of the nature of the crystal unit, correct handling is very important.

#### **Mechanical shock**

Crystal components are manufactured to withstand a certain level of mechanical shock. These levels are outlined within the environmental specifications for each individual component type throughout out the specification sheets.

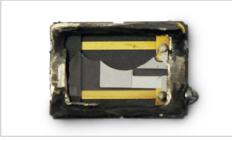

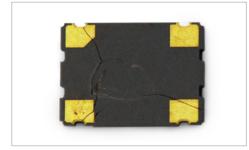

Excessive levels of shock can cause a change to the electrical characteristics, which will most likely manifest itself as a change of frequency. Severe mistreatment, such as dropping onto a hard surface, may well result in actual breakage of the quartz blank. In the case of ceramic packaged components it is also possible that the ceramic may crack, resulting in a loss of hermeticity.

Figure 1

Figure 3

Figure 2

## **Crystal Handling Precautions**

#### **Handling leads**

Excessive bending of leads can cause damage to the glass to metal seal, which can result in loss of hermeticity of the enclosure. Enclosures are filled with a dry inert gas and loss of hermeticity will result in a rapid deterioration of the product due to atmospheric contamination. Care should therefore be taken when handling a crystal not to pull or bend the leads. If the component needs to be moved in a way that involves bending, the lead should be bent slightly away from the glass seal to avoid cracking it. The recommended minimum radius of curvature is product dependent, e.g. 2 mm for HC49 crystals and 1mm for UM1s.

#### **Tape-and-reel product**

Before using crystal components on automated placement machines, tests should be undertaken to assess the level of shock that the crystal devices will be subjected to during the placement process. If necessary the shock level should be reduced.

Cracked HC49

#### Temperature

If crystals are subjected to extreme temperatures outside storage temperature limits, the electrical performance can be affected, resulting in eventual failure. During soldering it will be necessary to subject the components to high temperatures for limited periods of time, please refer to the RoHS Status of IQD Products document for maximum limiting values.

Broken Watch Crystal

#### Electrostatic discharge (ESD)

Only at extreme voltages can static electricity be seen, heard or even felt, but even the lowest voltages can damage electronic circuits. The damage caused to oscillators as a result of ESD may not immediately be evident but can be delayed, causing the oscillator circuitry to degrade, which in turn can cause failure of the oscillator in the field. Although quartz is not necessarily susceptible to ESD damage, the associated electronic circuitry contained within an oscillator is, and should be considered as an Electro Static Discharge Sensitive (ESDS) device. ESDS devices should only be handled in an ESD Protected Area (EPA), where proper precautions against ESD damage are taken.

## **Crystal Handling Precautions**

Any transportation should be undertaken using the appropriate protective packaging. All packaging should be marked with a warning notice, and protective measures and packaging should conform to BS EN 61340-5-1. For a more detailed breakdown of the precautions that should be taken, please contact our Customer Support Department.

#### Moisture Sensitivity Level protection

A small number of oscillators sold by IQD Frequency Products are sensitive to moisture ingress. This means that they can absorb moisture from the atmosphere, then during reflow soldering the moisture expands into steam and can crack the package thus resulting in permanent damage.

Levels of sensitivity to this type of damage are quantified with reference to JDEC-STD-020 and the relevant MSL level will be given on the device data sheet. On occasions when product is sensitive to this type of damage the product will arrive with you packaged and marked in accordance with JDEC-STD-033. Storage and handling of these products should continue to be performed in accordance with JDEC-STD-033 to avoid damage to the product during reflow.

Cracked Strip Resonator

Cracked Ceramic Package

Cracked 14-pin DIL

Bent Leads

# more than you expect

#### Würth Elektronik eiSos differs from all other component manufacturers in several aspects:

- We guarantee all catalogue products are manufactured to stock

- Samples free of charge

- Orders below MOQ

- Design kits with lifelong free refill

- Design Guide Trilogy of Magnetics, Trilogy of Connectors, Abc of Capacitors, Abc of Power Modules & Application Handbook The LTspice IV Simulator

- Design Seminars and Webinars free of charge

- Reference designs of leading IC manufacturers

- Worldwide technical sales force and field application engineers on site